# 12-Bit Monitor and Control System with Multichannel ADC, DACs, Temperature Sensor, and Current Sense

Data Sheet AD7294

## **FEATURES**

12-bit SAR ADC with 3 µs conversion time

4 uncommitted analog inputs

Differential/single-ended

$V_{REF}$ ,  $2 \times V_{REF}$  input ranges

2 high-side current sense inputs

5 V to 59.4 V operating range

0.5% max gain error

±200 mV input range

2 external diode temperature sensor inputs

-55°C to +150°C measurement range

±2°C accuracy

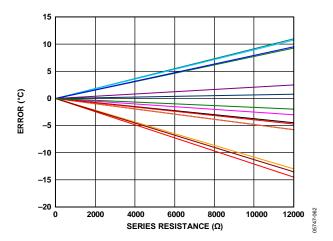

Series resistance cancellation

1 internal temperature sensor

±2°C accuracy

**Built-in monitoring features**

Minimum/maximum recorder for each channel

**Programmable alert thresholds**

**Programmable hysteresis**

Four 12-bit monotonic 15 V DACs

5 V span, 0 V to 10 V offset

8 µs settling time

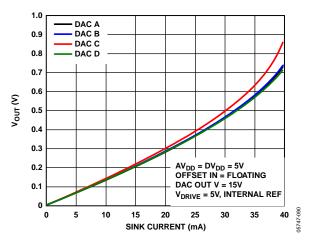

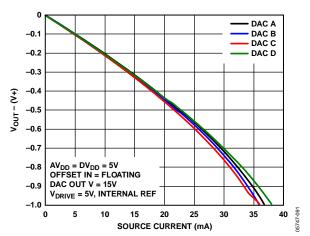

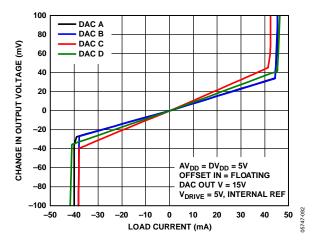

10 mA sink and source capability

Power-on resets (POR) to 0 V

Internal 2.5 V reference

2-wire fast mode I<sup>2</sup>C interface

Temperature range: -40°C to +105°C

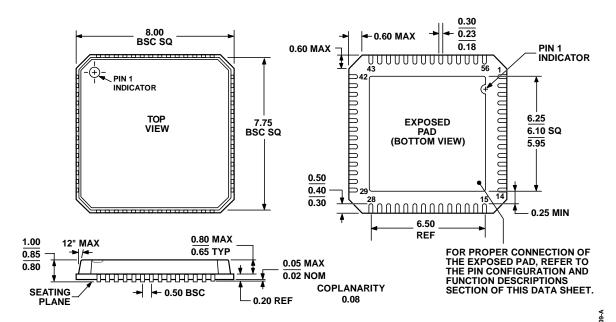

Package type: 64-lead TQFP or 56-lead LFCSP

#### **APPLICATIONS**

**Cellular base stations**

GSM, EDGE, UMTS, CDMA, TD-SCDMA, W-CDMA, WiMAX Point-to-multipoint and other RF transmission systems 12 V, 24 V, 48 V automotive applications Industrial controls

#### **GENERAL DESCRIPTION**

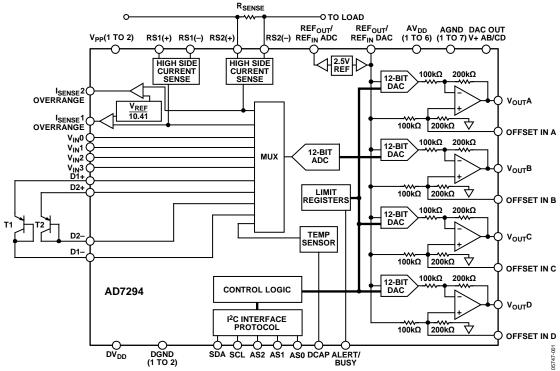

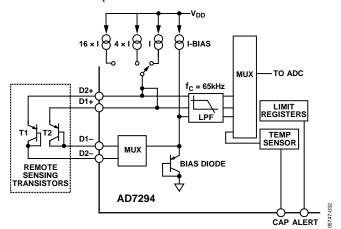

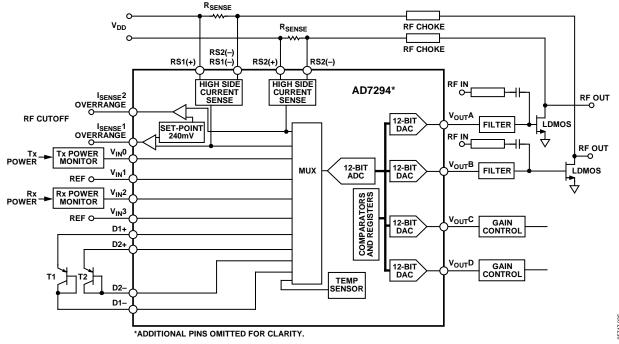

The AD7294 contains all the functions required for general-purpose monitoring and control of current, voltage, and temperature integrated into a single-chip solution. The part includes low voltage ( $\pm 200~\text{mV}$ ) analog input sense amplifiers for current monitoring across shunt resistors, temperature sense inputs, and four uncommitted analog input channels multiplexed into a SAR analog-to-digital converter (ADC) with a 3  $\mu$ s conversion time. A high accuracy internal reference is provided to drive both the digital-to-analog converter (DAC) and ADC. Four 12-bit DACs provide the outputs for voltage control. The AD7294 also includes limit registers for alarm functions. The part is designed on Analog Devices, Inc., high voltage DMOS process for high voltage compliance, 59.4 V on the current sense inputs, and up to a 15 V DAC output voltage.

The AD7294 is a highly integrated solution that offers all the functionality necessary for precise control of the power amplifier in cellular base station applications. In these types of applications, the DACs provide 12-bit resolution to control the bias currents of the power transistors. Thermal diode-based temperature sensors are incorporated to compensate for temperature effects. The ADC monitors the high-side current and temperature. All this functionality is provided in a 64-lead TQFP or a 56-lead LFCSP operating over a temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

## **IMPORTANT LINKS for the AD7294**\*

Last content update 11/16/2013 11:22 pm

## SIMILAR PRODUCTS & PARAMETRIC SELECTION TABLES

Find Similar Products By Operating Parameters

Low Resolution - Simultaneous Sampling 12-Bit PulSAR ADCs

Low Resolution - Muxed 8/10/12/13-Bit PulSAR ADCs

#### **EVALUATION KITS & SYMBOLS & FOOTPRINTS**

View the Evaluation Boards and Kits page for documentation and purchasing

Symbols and Footprints

#### **DOCUMENTATION**

**MS-2210:** Designing Power Supplies for High Speed ADC Multichannel I/O Data Converter Targets Basestations

Analog Devices IC Monitors Wireless Base Stations

Multichannel I/O Data Converter Targets Basestations

Brochure: Monitor and Control Solutions for Communications Systems

## **DESIGN COLLABORATION COMMUNITY**

<u>Collaborate Online</u> with the ADI support team and other designers about select ADI products.

Follow us on Twitter: <a href="https://www.twitter.com/ADL\_News">www.twitter.com/ADL\_News</a>

Like us on Facebook: <a href="https://www.facebook.com/AnalogDevicesInc">www.facebook.com/AnalogDevicesInc</a>

## SUGGESTED COMPANION PRODUCTS Recommended External References for the AD7294

- For applications requiring the lowest noise performance and output trim adjust, we recommend the <u>ADR441</u>.

- For high output current applications, we recommend the ADR431.

- For wide supply applications, we recommend the AD780.

- For cost sensitive applications, we suggest the AD1582 or the ADR391.

## **Recommended Driver Amplifiers for the AD7294**

- For applications requiring highest precision, we recommend the dual AD8606.

- For applications requiring low cost, low temperature drift, good DC and AC precision, we recommend the dual <u>AD8692</u>.

- For low power applications, we recommend the dual ADA4692-2.

- For high speed, low noise, low distortion, we recommend the dual AD8022.

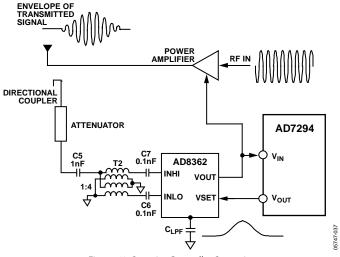

- For controlling a power amplifier in a cellular basestation application, we recommend the <u>AD8317</u> or the <u>AD8362</u>.

## **DESIGN SUPPORT**

Submit your support request here: <u>Linear and Data Converters</u> <u>Embedded Processing and DSP</u>

Telephone our Customer Interaction Centers toll free:

Americas: 1-800-262-5643 Europe: 00800-266-822-82 China: 4006-100-006 India: 1800-419-0108 Russia: 8-800-555-45-90

**Quality and Reliability Lead(Pb)-Free Data**

#### **SAMPLE & BUY**

## AD7294

- View Price & Packaging

- Request Evaluation Board

- Request Samples

- Check Inventory & Purchase

**Find Local Distributors**

## **TABLE OF CONTENTS**

| Features                                    | 1    |

|---------------------------------------------|------|

| Applications                                | 1    |

| General Description                         | 1    |

| Revision History                            | 3    |

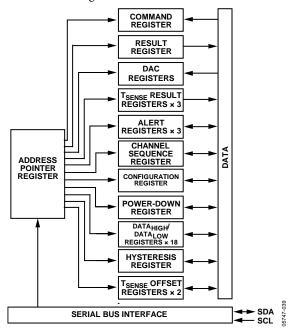

| Functional Block Diagram                    | 4    |

| Specifications                              | 5    |

| DAC Specifications                          | 5    |

| ADC Specifications                          | 6    |

| General Specifications                      | 8    |

| Timing Characteristics                      | 9    |

| Absolute Maximum Ratings                    | . 10 |

| Thermal Resistance                          | . 10 |

| ESD Caution                                 | . 10 |

| Pin Configuration and Function Descriptions | . 11 |

| Typical Performance Characteristics         | . 14 |

| Terminology                                 | . 19 |

| DAC Terminology                             | . 19 |

| ADC Terminology                             | . 19 |

| Theory of Operation                         | . 20 |

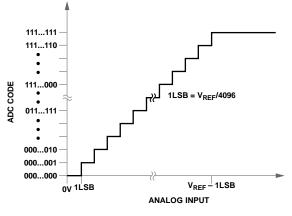

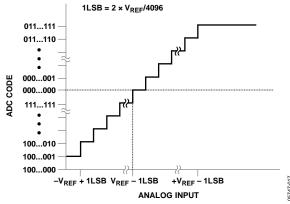

| ADC Overview                                | . 20 |

| ADC Transfer Functions                      | . 20 |

| Analog Inputs                               | . 20 |

| Current Sensor                              | . 22 |

| Analog Comparator Loop                      | . 23 |

| Temperature Sensor                          | . 24 |

| DAC Operation                               | . 25 |

| ADC and DAC Reference                       | . 25 |

| V <sub>DRIVE</sub> Feature                  | . 26 |

| Register Setting                            | . 27 |

| Address Pointer Register                    | . 27 |

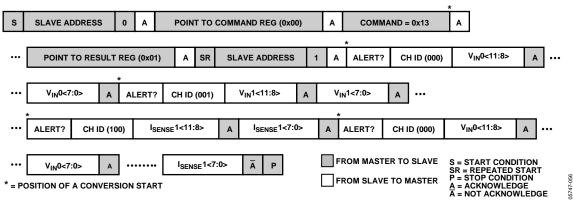

| Command Register (0x00)                     | . 28 |

| Result Register (0x01)                      | . 28 |

|                                             |      |

| T <sub>SENSE</sub> 1, T <sub>SENSE</sub> 2 Result Registers (0x02 and 0x03)29                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>SENSE</sub> INT Result Register (0x04)                                                                                                              |

| DAC <sub>A</sub> , DAC <sub>B</sub> , DAC <sub>C</sub> , DAC <sub>D</sub> , Registers (0x01 to 0x04)                                                       |

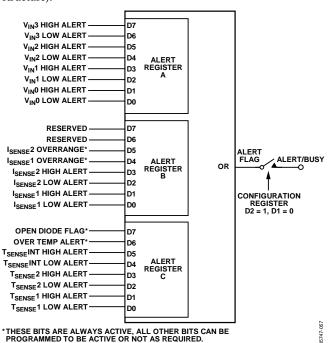

| Alert Status Register A (0x05), Register B (0x06), and Register C (0x07)30                                                                                 |

| Channel Sequence Register (0x08)                                                                                                                           |

| Configuration Register (0x09)31                                                                                                                            |

| Power-Down Register (0x0A)32                                                                                                                               |

| $ \begin{split} & DATA_{HIGH}/DATA_{LOW} \ Registers: 0x0B, 0x0C \ (V_{IN}0); 0x0E, 0x0F \\ & (V_{IN}1); 0x11, 0x12 \ (V_{IN}2); 0x14, 0x15 \ (V_{IN}3) \$ |

| Hysteresis Registers: 0x0D ( $V_{IN}$ 0), 0x10 ( $V_{IN}$ 1), 0x13 ( $V_{IN}$ 2), 0x16 ( $V_{IN}$ 3)32                                                     |

| T <sub>SENSE</sub> Offset Registers (0x26 and 0x27)                                                                                                        |

| I <sup>2</sup> C Interface                                                                                                                                 |

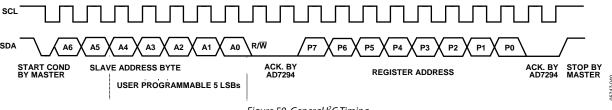

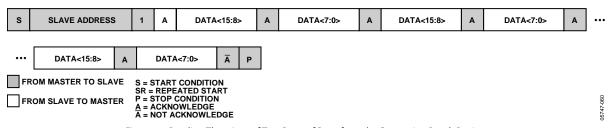

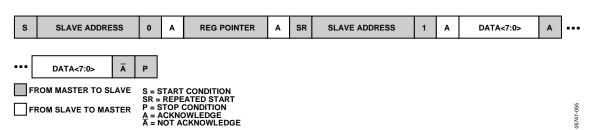

| General I <sup>2</sup> C Timing                                                                                                                            |

| Serial Bus Address Byte                                                                                                                                    |

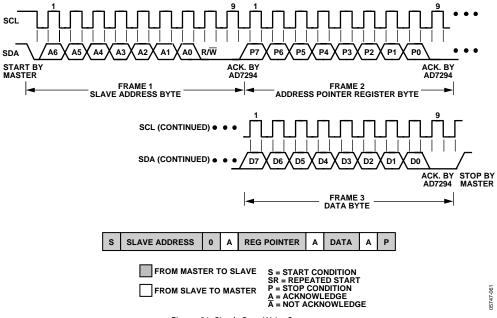

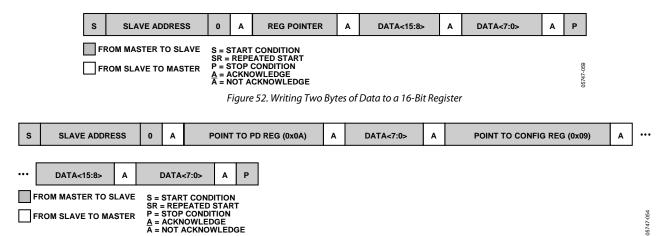

| Interface Protocol                                                                                                                                         |

| Modes of Operation                                                                                                                                         |

| Command Mode                                                                                                                                               |

| Autocycle Mode40                                                                                                                                           |

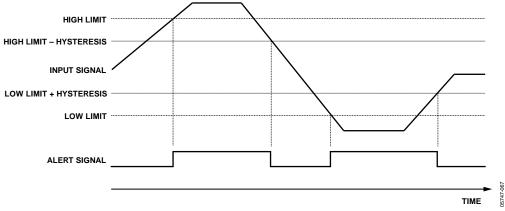

| Alerts and Limits Theory41                                                                                                                                 |

| Alert_Flag Bit41                                                                                                                                           |

| Alert Status Registers41                                                                                                                                   |

| Data <sub>HIGH</sub> and Data <sub>LOW</sub> Monitoring Features41                                                                                         |

| Hysteresis42                                                                                                                                               |

| Applications Information                                                                                                                                   |

| Base Station Power Amplifier Monitor and Control 43                                                                                                        |

| Gain Control of Power Amplifier44                                                                                                                          |

| Layout and Configuration                                                                                                                                   |

| Power Supply Bypassing and Grounding45                                                                                                                     |

| Outline Dimensions                                                                                                                                         |

| Ordering Guide 47                                                                                                                                          |

## **REVISION HISTORY**

| 1/12—Rev. G to Rev. H                                      |       |

|------------------------------------------------------------|-------|

| Changes to Table 2                                         | 6     |

| 11/11—Rev. F to Rev. G                                     |       |

| Change to DAC Output Characteristics Parameter of          |       |

| Table 1                                                    | 5     |

| Deleted DAC HIGH-Z Pin Leakage from Table 3                | 8     |

| Change to Figure 4                                         | 11    |

| Changes to Table 7                                         |       |

| Deleted Figure 47; Renumbered Sequentially                 | 25    |

| Deleted High Impedance Input Pin Section                   | 26    |

| 11/10—Rev. E to Rev. F                                     |       |

| Change to Table 2, Dynamic Performance, Spurious-Free      |       |

| Dynamic Range (SFDR)                                       | 6     |

| 10/10—Rev. D to Rev. E                                     |       |

| Change to Reflow Temperature, Table 5                      | 10    |

| 5/10—Rev. C to Rev. D                                      |       |

| Added 56-Lead LFCSPUniv                                    | ersal |

| Change to Features Section and General Description Section | n1    |

| Changes to Table 2                                         | 6     |

| Changes to Table 6                                         | 10    |

| Added Figure 4                                             | 11    |

## **FUNCTIONAL BLOCK DIAGRAM**

## **SPECIFICATIONS**

## **DAC SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 4.5 \text{ V}$  to 5.5 V, AGND = DGND = 0 V, internal 2.5 V reference;  $V_{DRIVE} = 2.7 \text{ V}$  to 5.5 V;  $T_A = -40 ^{\circ}\text{C}$  to +105 °C, unless otherwise noted. DAC OUTV+ AB and DAC OUTV+ CD = 4.5 V to 16.5 V, OFFSET IN x is floating, therefore, the DAC output span = 0 V to 5 V.

Table 1.

| Parameter                                       | Min  | Тур    | Max                | Unit   | Test Conditions/Comments                                                                                                                                                                       |

|-------------------------------------------------|------|--------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                        |      |        |                    |        |                                                                                                                                                                                                |

| Resolution                                      | 12   |        |                    | Bits   |                                                                                                                                                                                                |

| Relative Accuracy (INL)                         |      | ±1     | ±3                 | LSB    |                                                                                                                                                                                                |

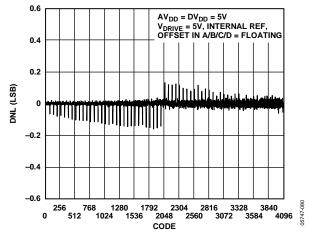

| Differential Nonlinearity (DNL)                 |      | ±0.3   | ±1                 | LSB    | Guaranteed monotonic                                                                                                                                                                           |

| Zero-Scale Error                                |      | 2.5    | 8                  | mV     |                                                                                                                                                                                                |

| Full-Scale Error of DAC and<br>Output Amplifier |      |        | 15.5 <sup>1</sup>  | mV     | DAC OUTV+ = 5.0 V                                                                                                                                                                              |

| Full-Scale Error of DAC                         |      | 2      |                    | mV     | DAC OUTV+ = 15.0 V                                                                                                                                                                             |

| Offset Error                                    |      |        | ±8.575             | mV     | Measured in the linear region, $T_A = -40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$                                                                                                           |

|                                                 |      |        | ±2                 | mV     | Measured in the linear region, $T_A = 25^{\circ}C$                                                                                                                                             |

| Offset Error Temperature<br>Coefficient         |      | ±5     |                    | ppm/°C |                                                                                                                                                                                                |

| Gain Error                                      |      | ±0.025 | ±0.155             | % FSR  |                                                                                                                                                                                                |

| Gain Temperature Coefficient                    |      | ±5     |                    | ppm/°C |                                                                                                                                                                                                |

| DAC OUTPUT CHARACTERISTICS                      |      |        |                    |        |                                                                                                                                                                                                |

| Output Voltage Span                             | 0    |        | $2 \times V_{REF}$ | V      | 0 V to 5 V for a 2.5 V reference                                                                                                                                                               |

| Output Voltage Offset                           | 0    |        | 10                 | V      | The output voltage span can be positioned in the 0 V to 15 V range; if the OFFSET IN x is left floating, the offset pin = $2/3 \times V_{REF}$ , giving an output of 0 V to $2 \times V_{REF}$ |

| Offset Input Pin Range                          | 0    |        | 5                  |        | $V_{OUT} = 3 V_{OFFSET} - 2 \times V_{REF} + V_{DAC}$                                                                                                                                          |

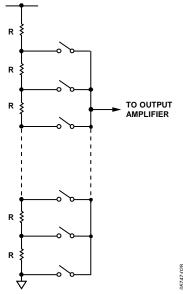

| DC Input Impedance <sup>2</sup>                 |      | 75     |                    | kΩ     | 100 k $\Omega$ to $V_{REF}$ , and 200 k $\Omega$ to AGND, see Figure 48                                                                                                                        |

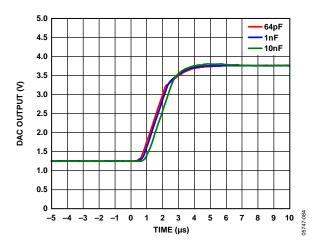

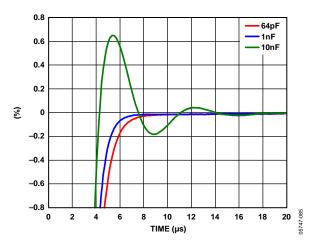

| Output Voltage Settling Time <sup>2</sup>       |      | 8      |                    | μs     | 1/4 to 3/4 change within 1/2 LSB, measured from last SCL edge                                                                                                                                  |

| Slew Rate <sup>2</sup>                          |      | 1.1    |                    | V/µs   |                                                                                                                                                                                                |

| Short-Circuit Current <sup>2</sup>              |      | 40     |                    | mA     | Full-scale current shorted to ground                                                                                                                                                           |

| Load Current <sup>2</sup>                       |      | ±10    |                    | mA     | Source and/or sink within 200 mV of supply                                                                                                                                                     |

| Capacitive Load Stability <sup>2</sup>          | 10   |        |                    | nF     | $R_L = \infty$                                                                                                                                                                                 |

| DC Output Impedance <sup>2</sup>                |      | 1      |                    | Ω      |                                                                                                                                                                                                |

| REFERENCE                                       |      |        |                    |        |                                                                                                                                                                                                |

| Reference Output Voltage                        | 2.49 | 2.5    | 2.51               | V      | $\pm 0.4\%$ maximum @ 25°C, AV <sub>DD</sub> = DV <sub>DD</sub> = 4.5 V to 5.5 V                                                                                                               |

| Reference Input Voltage Range                   | 0    |        | $AV_{DD} - 2$      | V      |                                                                                                                                                                                                |

| Input Current                                   |      | 100    | 125                | μΑ     | $V_{REF} = 2.5 \text{ V}$                                                                                                                                                                      |

| Input Capacitance <sup>2</sup>                  |      | 20     |                    | рF     |                                                                                                                                                                                                |

| V <sub>REF</sub> Output Impedance <sup>2</sup>  |      | 25     |                    | Ω      |                                                                                                                                                                                                |

| Reference Temperature<br>Coefficient            |      | 10     | 25                 | ppm/°C |                                                                                                                                                                                                |

<sup>&</sup>lt;sup>1</sup> This value indicates that the DAC output amplifiers can output voltages 15.5 mV below the DAC OUTV+ supply. If higher DAC OUTV+ supply voltages are used, the full-scale error of the DAC is typically 2 mV with no load

full-scale error of the DAC is typically 2 mV with no load.

<sup>2</sup> Samples are tested during initial release to ensure compliance; they are not subject to production testing.

## **ADC SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, \\ AGND = DGND = 0 \text{ V}, \\ V_{REF} = 2.5 \text{ V internal or external; } \\ V_{DRIVE} = 2.7 \text{ V to } 5.5 \text{ V}; \\ V_{PP} = AV_{DD} \text{ to } 59.4 \text{ V}; \\ T_{A} = -40 \text{°C to } +105 \text{°C}, \\ \text{unless otherwise noted.}$

Table 2.

| Parameter                                                | Min                 | Тур             | Max                 | Unit | Test Conditions/Comments                                                        |

|----------------------------------------------------------|---------------------|-----------------|---------------------|------|---------------------------------------------------------------------------------|

| DC ACCURACY                                              |                     |                 |                     |      |                                                                                 |

| Resolution                                               |                     | 12              |                     | Bits |                                                                                 |

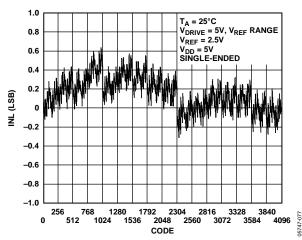

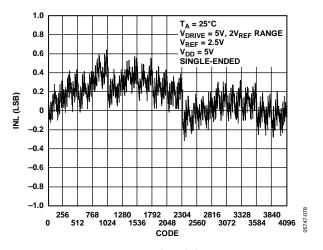

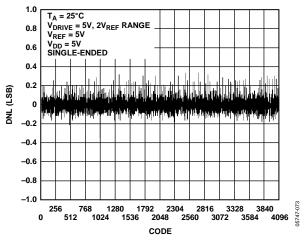

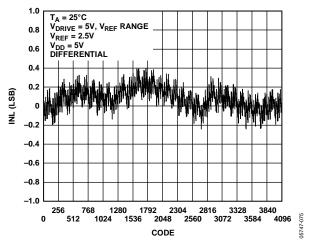

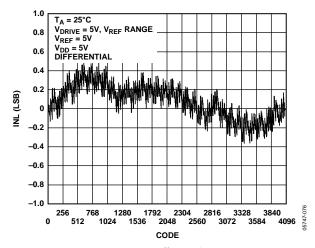

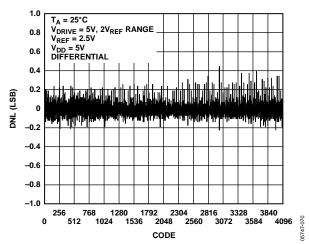

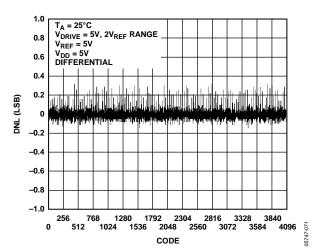

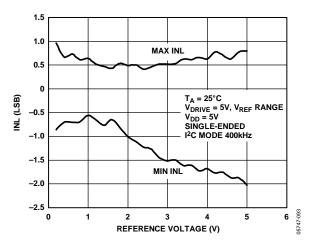

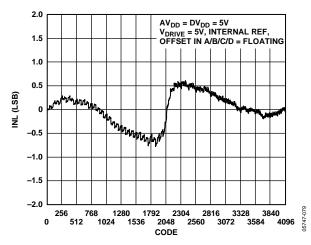

| Integral Nonlinearity (INL)1                             |                     | ±0.5            | ±1                  | LSB  | Differential mode                                                               |

| -                                                        |                     | ±0.5            | ±1.5                | LSB  | Single-ended or pseudo differential mode                                        |

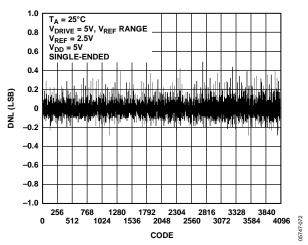

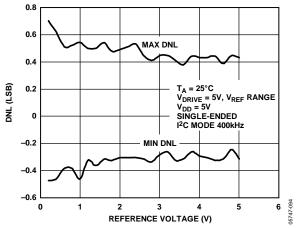

| Differential Nonlinearity (DNL) <sup>1</sup>             |                     | ±0.5            | ±0.99               | LSB  | Differential, single-ended, and pseudo differential modes                       |

| Single-Ended Mode                                        |                     |                 |                     |      |                                                                                 |

| Offset Error                                             |                     | ±1              | ±7                  | LSB  |                                                                                 |

| Offset Error Match                                       |                     | ±0.4            |                     | LSB  |                                                                                 |

| Gain Error                                               |                     | ±0.5            | ±2.5                | LSB  |                                                                                 |

| Gain Error Match                                         |                     | ±0.4            |                     | LSB  |                                                                                 |

| Differential Mode                                        |                     |                 |                     |      |                                                                                 |

| Positive Gain Error                                      |                     | ±1              |                     | LSB  |                                                                                 |

| Positive Gain Error Match                                |                     | ±0.5            |                     | LSB  |                                                                                 |

| Zero Code Error                                          |                     | ±3              |                     | LSB  |                                                                                 |

| Zero Code Error Match                                    |                     | ±0.5            |                     | LSB  |                                                                                 |

| Negative Gain Error                                      |                     | ±1              |                     | LSB  |                                                                                 |

| Negative Gain Error Match                                |                     | ±0.5            |                     | LSB  |                                                                                 |

| CONVERSION RATE                                          |                     |                 |                     |      |                                                                                 |

| Conversion Time <sup>2</sup>                             |                     | 3               |                     | μs   |                                                                                 |

| Autocycle Update Rate <sup>2</sup>                       |                     | 50              |                     | μs   |                                                                                 |

| Throughput Rate                                          |                     |                 | 22.22               | kSPS | $f_{SCL} = 400 \text{ kHz}$                                                     |

| ANALOG INPUT <sup>3</sup>                                |                     |                 |                     |      | JCL .                                                                           |

| Single-Ended Input Range                                 | 0                   |                 | $V_{REF}$           | ٧    | 0 V to V <sub>RFF</sub> mode                                                    |

| , J                                                      | 0                   |                 | $2 \times V_{RFF}$  | V    | 0 V to 2 × V <sub>RFF</sub> mode                                                |

| Pseudo Differential Input Range: $V_{IN+} - V_{IN-}^{4}$ | 0                   |                 | V <sub>REF</sub>    |      | 0 V to V <sub>REF</sub> mode                                                    |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                    | 0                   |                 | 2×V <sub>REF</sub>  |      | 0 V to 2 × V <sub>REF</sub> mode                                                |

| Fully Differential Input Range: $V_{IN+} - V_{IN-}$      | $-V_{REF}$          |                 | +V <sub>REF</sub>   |      | 0 V to V <sub>REF</sub> mode                                                    |

| · · · · · · · · · · · · · · · · · · ·                    | -2×V <sub>REF</sub> |                 | +2×V <sub>REF</sub> |      | 0 V to 2 × V <sub>REF</sub> mode                                                |

| Input Capacitance <sup>2</sup>                           | - · · · · REF       | 30              | · · · REF           | рF   | KEF WE SEE                                                                      |

| DC Input Leakage Current                                 |                     |                 | ±1                  | μΑ   |                                                                                 |

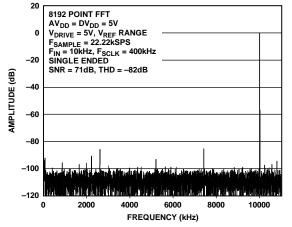

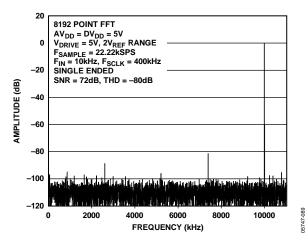

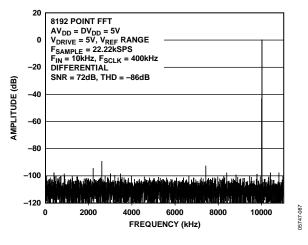

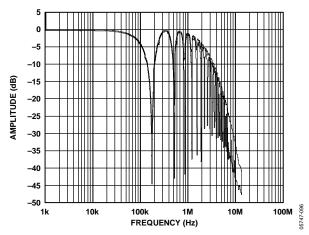

| DYNAMIC PERFORMANCE                                      |                     |                 |                     | Fr   |                                                                                 |

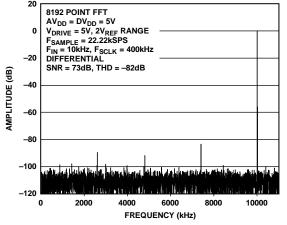

| Signal-to-Noise Ratio (SNR) <sup>1</sup>                 |                     | 73              |                     | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; differential mode                          |

| , , , , , , , , , , , , , , , , , , ,                    |                     | 72              |                     | dB   | f <sub>IN</sub> = 10 kHz sine wave; single-ended and pseudo differential modes  |

| Signal-to-Noise + Distortion (SINAD) Ratio <sup>1</sup>  | 1                   | 71.5            |                     | dB   | $f_{IN} = 10 \text{ kHz sine wave; differential mode}$                          |

| 2.3 to                                                   |                     | 72.5            |                     | dB   | $f_{IN} = 10$ kHz sine wave; single-ended and pseudo                            |

|                                                          |                     |                 |                     |      | differential modes                                                              |

| Total Harmonic Distortion (THD) <sup>1</sup>             |                     | -81             |                     | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; differential mode                          |

|                                                          |                     | <del>-</del> 79 |                     | dB   | $f_{IN}$ = 10 kHz sine wave; single-ended and pseudo differential modes         |

| Spurious-Free Dynamic Range (SFDR) <sup>1</sup>          | 1                   | -81             |                     | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; differential mode                          |

|                                                          |                     | -79             |                     |      | $f_{IN} = 10 \text{ kHz}$ sine wave; single-ended and pseudo differential modes |

| Channel-to-Channel Isolation <sup>2</sup>                | 1                   | -90             |                     | dB   | $f_{IN} = 10 \text{ kHz to } 40 \text{ kHz}$                                    |

| Parameter                                                                   | Min       | Тур  | Max           | Unit   | Test Conditions/Comments                                                                     |

|-----------------------------------------------------------------------------|-----------|------|---------------|--------|----------------------------------------------------------------------------------------------|

| TEMPERATURE SENSOR—INTERNAL                                                 |           |      |               |        |                                                                                              |

| Operating Range                                                             | -40       |      | +105          | °C     |                                                                                              |

| Accuracy                                                                    |           |      | ±2            | °C     | Internal temperature sensor, $T_A = -30^{\circ}\text{C}$ to $+90^{\circ}\text{C}$            |

|                                                                             |           |      | ±2.5          | °C     | Internal temperature sensor, $T_A = -40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$           |

| Resolution                                                                  |           | 0.25 |               | °C     | LSB size                                                                                     |

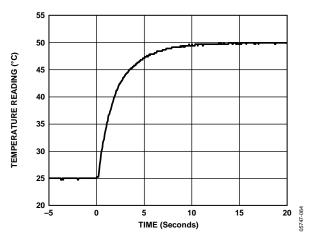

| Update Rate                                                                 |           | 5    |               | ms     |                                                                                              |

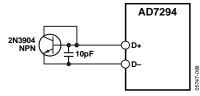

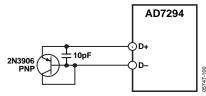

| TEMPERATURE SENSOR—EXTERNAL                                                 |           |      |               |        | External transistor is 2N3906                                                                |

| Operating Range                                                             | -55       |      | +150          | °C     | Limited by external diode                                                                    |

| Accuracy                                                                    |           |      | ±2            | °C     | $T_A = T_{DIODE} = -40^{\circ}C \text{ to } +105^{\circ}C$                                   |

| Resolution                                                                  |           | 0.25 |               | °C     | LSB size                                                                                     |

| Low Level Output Current Source <sup>2</sup>                                |           | 8    |               | μΑ     |                                                                                              |

| Medium Level Output Current Source <sup>2</sup>                             |           | 32   |               | μA     |                                                                                              |

| High Level Output Current Source <sup>2</sup>                               |           | 128  |               | μΑ     |                                                                                              |

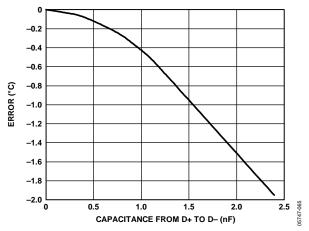

| Maximum Series Resistance (R <sub>s</sub> ) for External Diode <sup>2</sup> |           |      | 100           | Ω      | For $< \pm 0.5$ °C additional error, $C_p = 0$ , see Figure 31                               |

| Maximum Parallel Capacitance $(C_p)$ for External Diode <sup>2</sup>        |           |      | 1             | nF     | $R_S = 0$ , see Figure 30                                                                    |

| CURRENT SENSE                                                               |           |      |               |        | $V_{PP} = AV_{DD}$ to 59.4 V                                                                 |

| V <sub>PP</sub> Supply Range                                                | $AV_{DD}$ |      | 59.4          | V      |                                                                                              |

| Gain                                                                        | 12.4375   | 12.5 | 12.5625       |        | Gain of 12.5 gives a gain error = 0.5% maximum; delivers ±200 mV range with +2.5 V reference |

| RS(+)/RS(-) Input Bias Current                                              |           | 25   | 32            | μΑ     |                                                                                              |

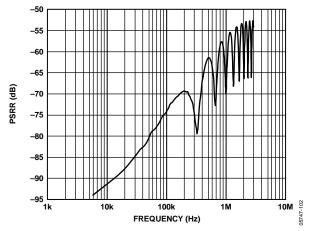

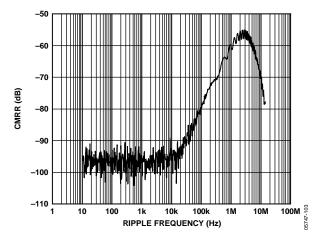

| CMRR/PSRR <sup>2</sup>                                                      |           | 80   |               | dB     | Inputs shorted to V <sub>PP</sub>                                                            |

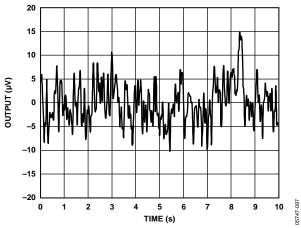

| Offset Error                                                                |           | ±50  | ±340          | μV     |                                                                                              |

| Offset Drift                                                                |           | 1    |               | μV/°C  |                                                                                              |

| Amplifier Peak-To-Peak Noise <sup>2</sup>                                   |           | 400  |               | μV     | Referred to input                                                                            |

| V <sub>PP</sub> Supply Current                                              |           | 0.18 | 0.25          | mA     | $V_{pp} = 59.4 \text{ V}$                                                                    |

| REFERENCE                                                                   |           |      |               |        |                                                                                              |

| Reference Output Voltage                                                    | 2.49      |      | 2.51          | V      | ±0.2% maximum at 25°C only                                                                   |

| Reference Input Voltage Range                                               | 0.1       |      | 4.1           | V      | For four uncommitted ADCs                                                                    |

|                                                                             | 1         |      | $AV_{DD} - 2$ |        | For current sense                                                                            |

| DC Leakage Current                                                          |           |      | ±2            | μΑ     |                                                                                              |

| V <sub>REF</sub> Output Impedance <sup>2</sup>                              |           | 25   |               | Ω      |                                                                                              |

| Input Capacitance <sup>2</sup>                                              |           | 20   |               | pF     |                                                                                              |

| Reference Temperature Coefficient                                           |           | 10   | 25            | ppm/°C |                                                                                              |

$<sup>^1</sup>$  See the Terminology section for more details.  $^2$  Sampled during initial release to ensure compliance, not subject to production testing.  $^3$  V $_{\rm IN+}$  or V $_{\rm IN-}$  must remain within GND/V $_{\rm DD}$ .  $^4$  V $_{\rm IN-}$  = 0 V for specified performance. For full input range on V $_{\rm IN-}$ , see Figure 40.

## **GENERAL SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, AGND = DGND = 0 \text{ V}, V_{REF} = 2.5 \text{ V internal or external; } V_{DRIVE} = 2.7 \text{ V to } 5.5 \text{ V}; V_{PP} = AV_{DD} \text{ to } 59.4 \text{ V}; DAC \text{ OUTV+ AB and DAC OUTV+ CD} = 4.5 \text{ V to } 16.5 \text{ V}; OFFSET \text{ IN x is floating, therefore, DAC output span} = 0 \text{ V to } 5 \text{ V}; T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 3.

| Parameter                                                                  | Min                               | Тур                 | Max                      | Unit | Test Conditions/Comments                                   |

|----------------------------------------------------------------------------|-----------------------------------|---------------------|--------------------------|------|------------------------------------------------------------|

| LOGIC INPUTS                                                               |                                   |                     |                          |      |                                                            |

| Input High Voltage, V <sub>IH</sub>                                        | 0.7 V <sub>DRIVE</sub>            |                     |                          | V    | SDA, SCL only                                              |

| Input Low Voltage, V <sub>⊩</sub>                                          |                                   |                     | 0.3 V <sub>DRIVE</sub>   | V    | SDA, SCL only                                              |

| Input Leakage Current, I <sub>IN</sub>                                     |                                   |                     | ±1                       | μΑ   |                                                            |

| Input Hysteresis, V <sub>HYST</sub>                                        | $0.05\mathrm{V}_{\mathrm{DRIVE}}$ |                     |                          | V    |                                                            |

| Input Capacitance, C <sub>IN</sub>                                         |                                   | 8                   |                          | pF   |                                                            |

| Glitch Rejection                                                           |                                   | 50                  |                          | ns   | Input filtering suppresses noise spikes of less than 50 ns |

| I <sup>2</sup> C® Address Pins Maximum External<br>Capacitance if Floating |                                   |                     | 30                       | pF   | Tristate input                                             |

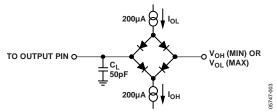

| LOGIC OUTPUTS                                                              |                                   |                     |                          |      |                                                            |

| SDA, ALERT                                                                 |                                   |                     |                          |      | SDA and ALERT/BUSY are open-drain outputs                  |

| Output Low Voltage, V <sub>OL</sub>                                        |                                   |                     | 0.4                      | V    | $I_{SINK} = 3 \text{ mA}$                                  |

|                                                                            |                                   |                     | 0.6                      | V    | $I_{SINK} = 6 \text{ mA}$                                  |

| Floating-State Leakage Current                                             |                                   |                     | ±1                       | μΑ   |                                                            |

| Floating-State Output Capacitance                                          |                                   | 8                   |                          | pF   |                                                            |

| I <sub>SENSE</sub> OVERRANGE                                               |                                   |                     |                          |      | I <sub>SENSE</sub> OVERRANGE is a push-pull output         |

| Output High Voltage, V <sub>OH</sub>                                       |                                   |                     | $V_{\text{DRIVE}} - 0.2$ | V    | $I_{SOURCE} = 200 \mu A$ for push-pull outputs             |

| Output Low Voltage, V <sub>OL</sub>                                        |                                   |                     | 0.2                      | V    | $I_{SINK} = 200 \mu A$ for push-pull outputs               |

| Overrange Setpoint                                                         | $V_{FS}$                          | $V_{FS} \times 1.2$ |                          | mV   | $V_{FS} = \pm V_{REF} ADC/12.5$                            |

| POWER REQUIREMENTS                                                         |                                   |                     |                          |      |                                                            |

| $V_{pp}$                                                                   | $AV_DD$                           |                     | 59.4                     | V    |                                                            |

| $AV_DD$                                                                    | 4.5                               |                     | 5.5                      | V    |                                                            |

| V(+)                                                                       | 4.5                               |                     | 16.5                     | V    |                                                            |

| $DV_{DD}$                                                                  | 4.5                               |                     | 5.5                      | V    | Tie DV <sub>DD</sub> to AV <sub>DD</sub>                   |

| $V_{DRIVE}$                                                                | 2.7                               |                     | 5.5                      | V    |                                                            |

| I <sub>DD</sub> Dynamic                                                    |                                   | 5.3                 | 6.5                      | mA   | $AV_{DD} + DV_{DD} + V_{DRIVE}$ , DAC outputs unloaded     |

| DAC OUTV+ x, I <sub>DD</sub>                                               |                                   | 0.6                 | 1.2                      | mA   | @ midscale output voltage, DAC outputs unloaded            |

| Power Dissipation                                                          |                                   | 70                  | 105                      | mW   |                                                            |

| Power-Down                                                                 |                                   |                     |                          |      |                                                            |

| I <sub>DD</sub>                                                            |                                   | 0.5                 | 1                        | μΑ   | For each AV <sub>DD</sub> and V <sub>DRIVE</sub>           |

| $DI_DD$                                                                    |                                   | 1                   | 16.5                     | μΑ   |                                                            |

| DAC OUTV+ x, I <sub>DD</sub>                                               |                                   | 35                  | 60                       | μΑ   |                                                            |

| Power Dissipation                                                          |                                   |                     | 2.5                      | mW   |                                                            |

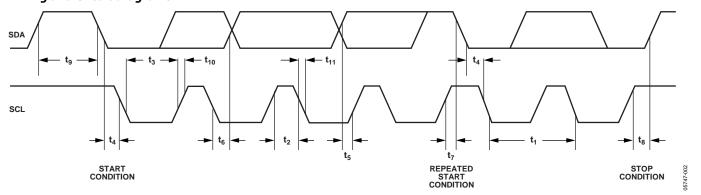

## **TIMING CHARACTERISTICS**

## I<sup>2</sup>C Serial Interface

$AV_{DD} = DV_{DD} = 4.5 \text{ V}$  to 5.5 V, AGND = DGND = 0 V,  $V_{REF} = 2.5 \text{ V}$  internal or external;  $V_{DRIVE} = 2.7 \text{ V}$  to 5.5 V;  $V_{PP} = AV_{DD}$  to 59.4 V; DAC OUTV+ AB and DAC OUTV+ CD = 4.5 V to 16.5 V; OFFSET IN x is floating, therefore, DAC output span = 0 V to 5 V;  $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , unless otherwise noted.

Table 4.

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                                                |

|------------------------|----------------------------------------------|---------|----------------------------------------------------------------------------|

| f <sub>SCL</sub>       | 400                                          | kHz max | SCL clock frequency                                                        |

| t <sub>1</sub>         | 2.5                                          | μs min  | SCL cycle time                                                             |

| $t_2$                  | 0.6                                          | μs min  | t <sub>HIGH</sub> , SCL high time                                          |

| t <sub>3</sub>         | 1.3                                          | μs min  | t <sub>LOW</sub> , SCL low time                                            |

| t <sub>4</sub>         | 0.6                                          | μs min  | t <sub>HD,STA</sub> , start/repeated start condition hold time             |

| t <sub>5</sub>         | 100                                          | ns min  | t <sub>SU,DAT</sub> , data setup time                                      |

| t <sub>6</sub>         | 0.9                                          | μs max  | t <sub>HD,DAT</sub> , data hold time                                       |

|                        | 0                                            | μs min  | t <sub>HD,DAT</sub> , data hold time                                       |

| t <sub>7</sub>         | 0.6                                          | μs min  | t <sub>SU,STA</sub> , setup time for repeated start                        |

| t <sub>8</sub>         | 0.6                                          | μs min  | t <sub>SU,STO</sub> , stop condition setup time                            |

| t <sub>9</sub>         | 1.3                                          | μs min  | t <sub>BUF</sub> , bus free time between a stop and a start condition      |

| t <sub>10</sub>        | 300                                          | ns max  | t <sub>R</sub> , rise time of SCL and SDA when receiving                   |

|                        | 0                                            | ns min  | t <sub>R</sub> , rise time of SCL and SDA when receiving (CMOS compatible) |

| t <sub>11</sub>        | 300                                          | ns max  | t <sub>F</sub> , fall time of SDA when transmitting                        |

|                        | 0                                            | ns min  | t <sub>F</sub> , fall time of SDA when receiving (CMOS compatible)         |

|                        | 300                                          | ns max  | t <sub>F</sub> , fall time of SCL and SDA when receiving                   |

|                        | $20 + 0.1C_b^2$                              | ns min  | t <sub>F</sub> , fall time of SCL and SDA when transmitting                |

| C <sub>b</sub>         | 400                                          | pF max  | Capacitive load for each bus line                                          |

<sup>&</sup>lt;sup>1</sup> See Figure 2.

## **Timing and Circuit Diagrams**

Figure 2. I<sup>2</sup>C-Compatible Serial Interface Timing Diagram

Figure 3. Load Circuit for Digital Output

$<sup>^{2}</sup>$  C<sub>D</sub> is the total capacitance in pF of one bus line.  $t_{R}$  and  $t_{F}$  are measured between 0.3 DV<sub>DD</sub> and 0.7 DV<sub>DD</sub>.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.<sup>1</sup>

Table 5.

| Table 3.                                          |                                                              |

|---------------------------------------------------|--------------------------------------------------------------|

| Parameter                                         | Rating                                                       |

| V <sub>PP</sub> x to AGND                         | −0.3 V to +70 V                                              |

| AV <sub>DD</sub> x to AGND                        | −0.3 V to +7 V                                               |

| DAC OUTV+ AB to AGND                              | −0.3 V to +17 V                                              |

| DAC OUTV+ CD to AGND                              | −0.3 V to +17 V                                              |

| DV <sub>DD</sub> to DGND                          | −0.3 V to +7 V                                               |

| $V_{DRIVE}$ to OPGND                              | −0.3 V to +7 V                                               |

| Digital Inputs to OPGND                           | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$                |

| SDA/SCL to OPGND                                  | −0.3 V to +7 V                                               |

| Digital Outputs to OPGND                          | $-0.3  \text{V} \text{ to V}_{\text{DRIVE}} + 0.3  \text{V}$ |

| $RS(+)/RS(-)$ to $V_{PP}x$                        | $V_{pp} - 0.3 \text{ V to } V_{pp} + 0.3 \text{ V}$          |

| REF <sub>OUT</sub> /REF <sub>IN</sub> ADC to AGND | $-0.3  \text{V} \text{ to AV}_{\text{DD}} + 0.3  \text{V}$   |

| REF <sub>OUT</sub> /REF <sub>IN</sub> DAC to AGND | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                  |

| OPGND to AGND                                     | -0.3 V to +0.3 V                                             |

| OPGND to DGND                                     | −0.3 V to +0.3 V                                             |

| AGND to DGND                                      | −0.3 V to +0.3 V                                             |

| V <sub>OUT</sub> x to AGND                        | -0.3 V to DAC OUTV(+) + 0.3 V                                |

| Analog Inputs to AGND                             | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                  |

| Operating Temperature Range                       |                                                              |

| B Version                                         | −40°C to +105°C                                              |

| Storage Temperature Range                         | −65°C to +150°C                                              |

| Junction Temperature (T <sub>J</sub> Max)         | 150°C                                                        |

| ESD Human Body Model                              | 1 kV                                                         |

| Reflow Soldering Peak                             | 260°C                                                        |

| Temperature                                       |                                                              |

$<sup>^{\</sup>rm 1}$  Transient currents of up to 100 mA do not cause SCR latch-up.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

To conform with IPC 2221 industrial standards, it is advisable to use conformal coating on the high voltage pins.

## THERMAL RESISTANCE

Table 6. Thermal Resistance

| Package Type  | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|---------------|---------------|-----------------|------|

| 64-Lead TQFP  | 54            | 16              | °C/W |

| 56-Lead LFCSP | 21            | 2               | °C/W |

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

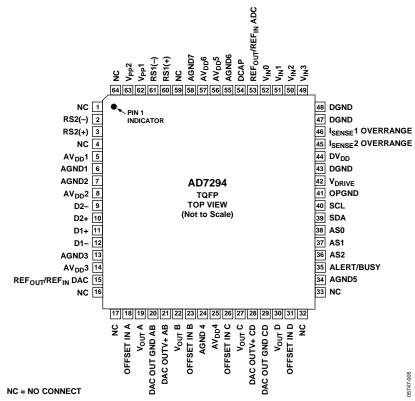

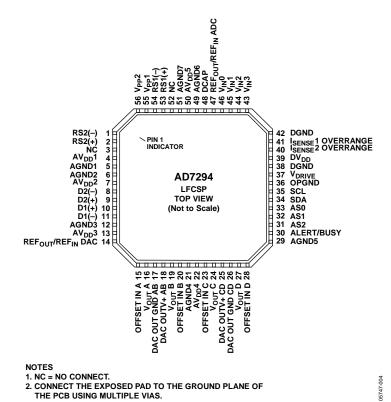

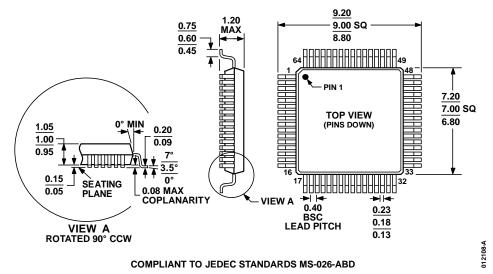

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. TQFP Pin Configuration

Figure 5. LFCSP Pin Configuration

Table 7. Pin Function Descriptions

TOFP Pin No. LFCSP Pin No.

| TQFP Pin No.                    | LFCSP Pin No.              | Mnemonic                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------|----------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 61                           | 1, 54                      | RS2(-), RS1(-)                                                           | Connection for External Shunt Resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3, 60                           | 2, 53                      | RS2(+), RS1(+)                                                           | Connection for External Shunt Resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1, 4, 16, 17, 32,<br>33, 59, 64 | 3, 52                      | NC                                                                       | No Connection. Do not connect these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5, 8, 14, 25, 56, 57            | 4, 7, 13, 22, 50           | AV <sub>DD</sub> 1 to AV <sub>DD</sub> 6<br>for TQFP; AV <sub>DD</sub> 1 | Analog Supply Pins. The operating range is 4.5 V to 5.5 V. These pins provide the supply voltage for all the analog circuitry on the AD7294. Connect the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                            | to AV <sub>DD</sub> 4 for<br>LFCSP                                       | AV <sub>DD</sub> and DV <sub>DD</sub> pins together to ensure that all supply pins are at the same potential. This supply should be decoupled to AGND with one 10 $\mu$ F tantalum capacitor and a 0.1 $\mu$ F ceramic capacitor for each AV <sub>DD</sub> pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6, 7, 13, 24, 34,<br>55, 58     | 5, 6 12, 21, 29, 49,<br>51 | AGND1 to<br>AGND7                                                        | Analog Ground. Ground reference point for all analog circuitry on the AD7294. Refer all analog input signals and any external reference signal to this AGND voltage. Connect all seven of these AGND pins to the AGND plane of the system. Note that AGND5 is a DAC ground reference point and should be used as a star ground for circuitry being driven by the DAC outputs. Ideally, the AGND and DGND voltages should be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                     |

| 9, 12                           | 8, 11                      | D2(-), D1(-)                                                             | Temperature Sensor Analog Input. These pins are connected to the external temperature sensing transistor. See Figure 46 and Figure 47.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10, 11                          | 9, 10                      | D2(+), D1(+)                                                             | Temperature Sensor Analog Input. These pins are connected to the external temperature sensing transistor. See Figure 46 and Figure 47.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15                              | 14                         | REF <sub>OUT</sub> /REF <sub>IN</sub> DAC                                | DAC Reference Output/Input Pin. The REF <sub>OUT</sub> /REF <sub>IN</sub> DAC pin is common to all four DAC channels. On power-up, the default configuration of this pin is external reference (REF <sub>IN</sub> ). Enable the internal reference by writing to the power-down register; see Table 27. Decoupling capacitors (220 nF recommended) are connected to this pin to decouple the reference buffer. Provided the output is buffered, the on-chip reference can be taken from this pin and applied externally to the rest of a system. A maximum external reference voltage of AV <sub>DD</sub> – 2 V can be supplied to the REF <sub>OUT</sub> portion of the REF <sub>OUT</sub> /REF <sub>IN</sub> DAC pin. |

| 18, 23, 26, 31                  | 15, 20 23,28               | OFFSET IN A to<br>OFFSET IN D                                            | DAC Analog Offset Input Pins. These pins set the desired output range for each DAC channel. The DACs have an output voltage span of 5 V, which can be shifted from 0 V to 5 V to a maximum output voltage of 10 V to 15 V by supplying an offset voltage to these pins. These pins can be left floating, in which case decouple them to AGND with a 100 nF capacitor.                                                                                                                                                                                                                                                                                                                                                   |

| 19, 22, 27, 30                  | 16, 19, 24, 27             | V <sub>OUT</sub> A to V <sub>OUT</sub> D                                 | Buffered Analog DAC Outputs for Channel A to Channel D. Each DAC analog output is driven from an output amplifier that can be offset using the OFFSET IN x pin. The DAC has a maximum output voltage span of 5 V that can be level shifted to a maximum output voltage level of 15 V. Each output is capable of sourcing and sinking 10 mA and driving a 10 nF load.                                                                                                                                                                                                                                                                                                                                                    |

| 20, 29                          | 17, 26                     | DAC OUT GND<br>AB, DAC OUT<br>GND CD                                     | Analog Ground. Analog ground pins for the DAC output amplifiers on $V_{\text{OUT}}A$ and $V_{\text{OUT}}B$ , and $V_{\text{OUT}}C$ and $V_{\text{OUT}}D$ , respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21, 28                          | 18, 25                     | DAC OUTV+ AB,<br>DAC OUTV+ CD                                            | Analog Supply. Analog supply pins for the DAC output amplifiers on $V_{OUT}A$ and $V_{OUT}B$ , and $V_{OUT}C$ and $V_{OUT}D$ , respectively. The operating range is 4.5 V to 16.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 35                              | 30                         | ALERT/BUSY                                                               | Digital Output. Selectable as an alert or busy output function in the configuration register. This is an open-drain output. An external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 |                            |                                                                          | When configured as an alert, this pin acts as an out-of-range indicator and becomes active when the conversion result violates the DATA <sub>HIGH</sub> or DATA <sub>LOW</sub> register values. See the Alert Status Registers section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20.27.25                        | 22.22.25                   | 160 164 165                                                              | When configured as a busy output, this pin becomes active when a conversion is in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 38, 37, 36                      | 33, 32, 31                 | ASO, AS1, AS2                                                            | Digital Logic Input. Together, the logic state of these inputs selects a unique I <sup>2</sup> C address for the AD7294. See Table 34 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 39                              | 34                         | SDA                                                                      | Digital Input/Output. Serial bus bidirectional data; external pull-up resistor required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TQFP Pin No.   | LFCSP Pin No.  | Mnemonic                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

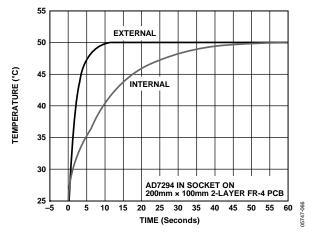

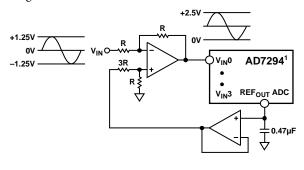

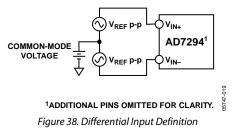

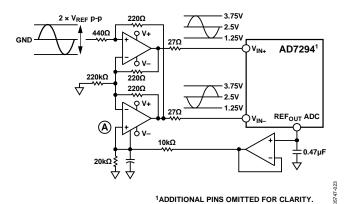

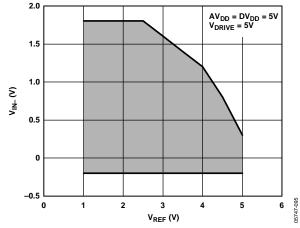

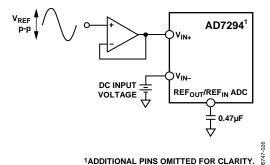

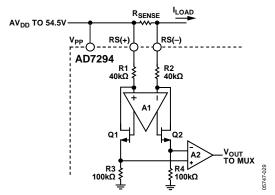

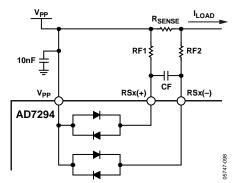

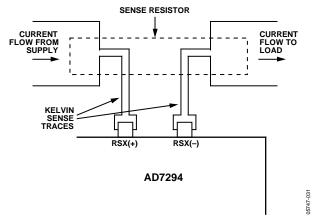

| 40             | 35             | SCL                                                        | Serial I <sup>2</sup> C Bus Clock. The data transfer rate in I <sup>2</sup> C mode is compatible with both 100 kHz and 400 kHz operating modes. Open-drain input; external pull-up resistor required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |