### 680-920 MHz High IP3 Dual Channel Downconverter SEMICONDUCTOR

#### **Applications**

- 3G / 4G Wireless Infrastructure

- CDMA, WCDMA, LTE, TD-LTE

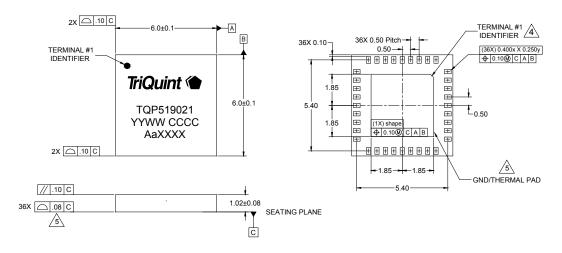

36-pin 6x6 mm Leadless Package

#### **Product Features**

- High dynamic range

- · Integrated LO/IF amplifiers and LO Switch

- · Dual Channels for diversity

- RF Frequency Range : 680-920 MHz

- IF Frequency Range: 70-280 MHz

- 9 dB Conversion Gain

- 25.5 dBm Input IP3

- 10.8 dB Noise Figure

- 11.8 dBm Input P1dB

- Built-in high isolation LO Switch

- Power Shut-down Mode

- Optional Low Current Mode for IF amplifiers

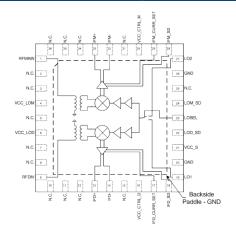

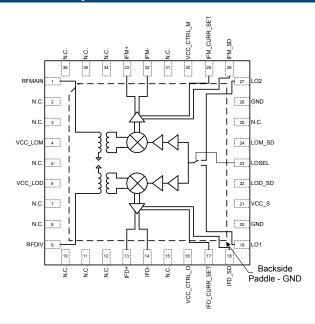

#### **Functional Block Diagram**

#### **General Description**

The TQP519021 is a high-linearity dual-channel down-converter designed to meet the demanding performance, functionality, and cost goals of current and next generation mobile infrastructure base-stations. It provides high dynamic range performance in a low profile lead-free/RoHS-compliant surface-mount leadless package that measures 6x6 mm square.

The TQP519021 is a fully integrated diversity mixer that includes LO switch, two stage LO drivers, high-linearity mixers, RF balun and IF amplifiers. The IF amplifiers can be set to standard current or low current mode through logic input pins. The TQP519021 also integrates power down feature controlled by separate logic pin.

The TQP519021 is designed to provide 9 dB conversion gain, +25.5 dBm Input IP3, +11.8 dBm Input P1dB and a noise figure of 10.8 dB over the 680-920MHz frequency range for diversity receiver applications. TQP519021 is optimized for low side LO application but also works for High-side LO applications with slightly degraded linearity performance. The TQP519021 is footprint and pin compatible with TriQuint's 1.7-2.2 GHz TQP569022 mixer for high band applications.

#### **Pin Configuration**

| Pin#   | Symbol       | Pin#       | Symbol       |

|--------|--------------|------------|--------------|

| 1      | RFMAIN       | 22         | LOD_SD       |

| 4      | VCC_LOM      | 23         | LOSEL        |

| 6      | VCC_LOD      | 24         | LOM_SD       |

| 9      | RFDIV        | 27         | LO2          |

| 13, 14 | IFD+ , IFD-  | 28         | IFM_SD       |

| 16     | VCC_CTRL_D   | 29         | IFM_CURR_SET |

| 17     | IFD_CURR_SET | 30         | VCC_CTRL_M   |

| 18     | IFD_SD       | 32,33      | IFM+, IFM-   |

| 19     | LO1          | 20, 26     | RF GND       |

| 21     | VCC          | All Others | NC or GND    |

### Ordering Information

| Part No.      | Description                |

|---------------|----------------------------|

| TQP519021     | Dual-channel Downconverter |

| TQP519021-PCB | Assembled Evaluation Board |

Standard T/R size = 2500 pieces on a 13" reel.

Data Sheet: Rev C 12/20/2012 © 2012 TriQuint Semiconductor. Inc. - 1 of 14 -

Disclaimer: Subject to change without notice

## 680-920 MHz High IP3 Dual Channel Downconverter SEMICONDUCTOR

### **Absolute Maximum Ratings**

| Parameter                                          | Rating       |

|----------------------------------------------------|--------------|

| Storage Temperature                                | -55 to 150°C |

| RF Input Power, CW, $50\Omega$ ,T = $25^{\circ}$ C | +15 dBm      |

| LO Input Power CW, $50\Omega$ ,T = $25^{\circ}$ C  | +5 dBm       |

| Vcc (pins 4, 6, 21)<br>Vctrl (pins 16, 30)         | +5.5 V       |

Operation of this device outside the parameter ranges given above may cause permanent damage.

#### **Recommended Operating Conditions**

| Parameter                                        | Min | Тур | Max  | Units |

|--------------------------------------------------|-----|-----|------|-------|

| Vcc (pins 4, 6, 21)                              | 3.3 | 5   | 5.25 | V     |

| T <sub>CASE</sub>                                | -40 |     | +85  | °C    |

| T <sub>J</sub> (for >10 <sup>6</sup> hours MTTF) |     |     | 190  | °C    |

| LO Power                                         | -3  | 0   | +3   | dBm   |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

#### **Electrical Specifications**

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 680 MHz, IF = 140 MHz

| Parameter                                   | Conditions                        | Min   | Тур   | Max  | Units |

|---------------------------------------------|-----------------------------------|-------|-------|------|-------|

| RF Frequency Range                          |                                   | 680   |       | 920  | MHz   |

| LO Frequency Range                          |                                   | 600   |       | 1100 | MHz   |

| IF Frequency Range                          |                                   | 70    | 140   | 280  | MHz   |

| Conversion Gain                             | Standard Current Mode             | 7.5   | 9     | 11.5 | dB    |

| Conversion Gain                             | Low Current Mode                  | 6.5   | 8     | 10.5 | dB    |

| Gain Flatness                               |                                   |       | ± 0.5 |      | dB    |

| Gain Variation over temp                    | -40 to +85°C, referenced to +25°C |       | ±1.0  |      | dB    |

| Input IP3                                   | Standard Current Mode             | +22.5 | +25.5 |      | dBm   |

| Pin = -10dBm/tone, $\Delta f$ = 1MHz        | Low Current Mode                  | +16   | +20   |      | dBm   |

| Input IP3 Variation over temp               | -40 to +85°C, referenced to +25°C |       | ±1.0  |      | dB    |

| Input IP2                                   | Standard Current Mode             |       | +65   |      | dBm   |

| Pin = -10dBm/tone                           | Low Current Mode                  |       | +65   |      | dBm   |

| Input D1dD                                  | Standard Current Mode             |       | +11.8 |      | dBm   |

| Input P1dB                                  | Low Current Mode                  |       | +7.3  |      | dBm   |

| SSB Noise Figure                            |                                   |       | 10.8  |      | dB    |

| SSB Noise Figure over temp                  | -40 to +85°C, referenced to +25°C |       | ±1.3  |      | dB    |

| Noise Figure with Blocker                   | Pblocker = 8dBm, RF = 860MHz      |       | 18.6  |      | dB    |

| 2LO-2RF Spur Rejection<br>Pin = -10dBm/tone |                                   |       | 75    |      | dBc   |

| 3LO-3RF Spur Rejection                      | Standard Current Mode             |       | 90    |      | dBc   |

| Pin = -10dBm/tone                           | Low Current Mode                  |       | 80    |      | dBc   |

| LO Leakage at RF port                       |                                   |       | -33   |      | dBm   |

| LO Leakage at IF port                       |                                   |       | -50   |      | dBm   |

| LO2-LO1 Isolation                           |                                   | 40    | 48    |      | dB    |

| Channel to Channel Isolation                |                                   |       | 53    |      | dB    |

| RF-IF Isolation                             |                                   |       | 25    |      | dB    |

| RF Return Loss                              |                                   |       | 12    |      | dB    |

| LO Return Loss                              |                                   |       | 10    |      | dB    |

| IF Return Loss                              | With ext. IF balun TC4-1W-17LN+   |       | 15    |      | dB    |

Data Sheet: Rev C 12/20/2012 © 2012 TriQuint Semiconductor, Inc. - 2 of 14 -

Disclaimer: Subject to change without notice

Connecting the Digital World to the Global Network®

## **Electrical Specifications (contd.)**

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 680 MHz, IF = 140 MHz

| Parameter                           | Conditions            | Min | Тур  | Max | Units |

|-------------------------------------|-----------------------|-----|------|-----|-------|

| IF differential port impedance      |                       |     | 200  |     | Ohms  |

|                                     | Standard Current Mode | 240 | 295  | 350 | mA    |

| Total Supply Current                | Low Current Mode      | 150 | 195  | 250 | mA    |

|                                     | Shut Down Mode        |     | 3.5  |     | mA    |

| Logic Low Voltage                   |                       | 0   |      | 0.4 | V     |

| Logic High Voltage                  |                       | 1.4 |      | Vcc | V     |

| LO Switching Time                   |                       |     | 100  |     | ns    |

| Logic Input Current                 | At 5V Logic High      |     | 50   |     | μA    |

| Thermal Resistance, θ <sub>jc</sub> | Junction to Case      |     | 23.4 |     | °C/W  |

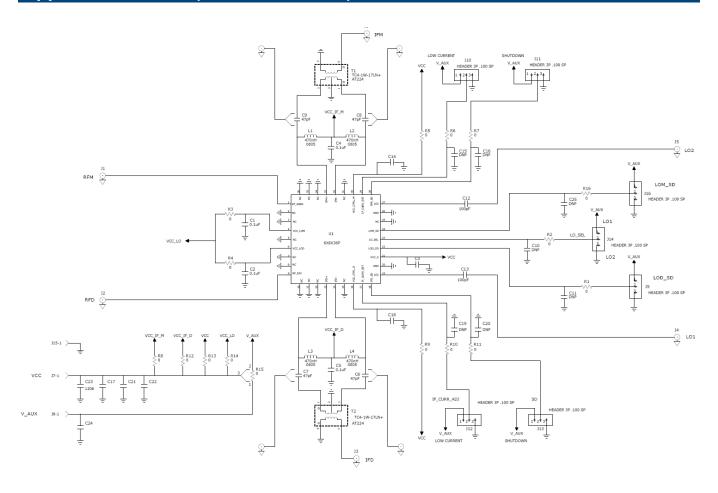

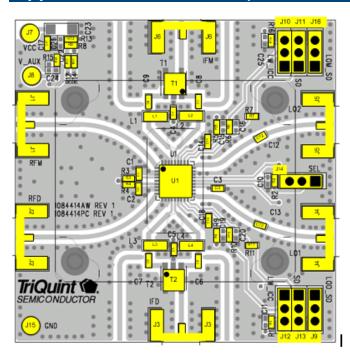

### **Application Circuit (TQP519021-PCB)**

## **Application Circuit Board (TQP519021-PCB)**

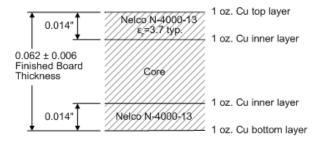

#### PCB Material and Stack-up

#### Bill of Material - TQP3M9035-PCB

| Reference Des.                                                        | Value  | Description                 | Manuf.        | Part Number   |

|-----------------------------------------------------------------------|--------|-----------------------------|---------------|---------------|

| U1                                                                    |        | Downconverter               | TriQuint      | TQP519021     |

| R1, R2, R3, R4, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, R16 | 0 Ω    | RES, 0402, 5%, 1/16W, Chip  | Various       |               |

| C1, C2, C3, C4, C5, C14, C17, C18                                     | 0.1 uF | CAP, 0402, 5%, 50V, NPO     | Various       |               |

| C6, C7, C8, C9                                                        | 47 pF  | CAP, 0402, 5%, 50V, NPO     | Various       |               |

| C12, C13                                                              | 100 pF | CAP, 0402, 5%, 50V, NPO/COG | Various       |               |

| T1, T2                                                                |        | RF Transformer              | Mini-Circuits | TC4-1W-17LN+  |

| L1, L2, L3, L4                                                        | 470 nH | IND, 0805, 5%, Ceramic Core | Coilcraft     | 0805CS-471XJL |

| C10, C11, C15, C16, C19, C20, C21, C22, C23, C24, C25                 |        | Do Not Place                |               |               |

## **Jumper Settings - TQP3M9035-PCB**

| Jumper | Pin No. | Function     | Low High              |                  |

|--------|---------|--------------|-----------------------|------------------|

| J9     | 22      | LOD_SD       | Operation Mode        | Shutdown Mode    |

| J10    | 29      | IFM_CURR_SET | Standard Current Mode | Low Current Mode |

| J11    | 28      | IFM_SD       | Operation Mode        | Shutdown Mode    |

| J12    | 17      | IFD_CURR_SET | Standard Current Mode | Low Current Mode |

| J13    | 18      | IFD_SD       | Operation Mode        | Shutdown Mode    |

| J14    | 23      | LOSEL        | LO2                   | LO1              |

| J16    | 24      | LOM_SD       | Operation Mode        | Shutdown Mode    |

Data Sheet: Rev C 12/20/2012 © 2012 TriQuint Semiconductor, Inc. - 4 of 14 - Disclaimer: Subject to change without notice

Connecting the Digital World to the Global Network®

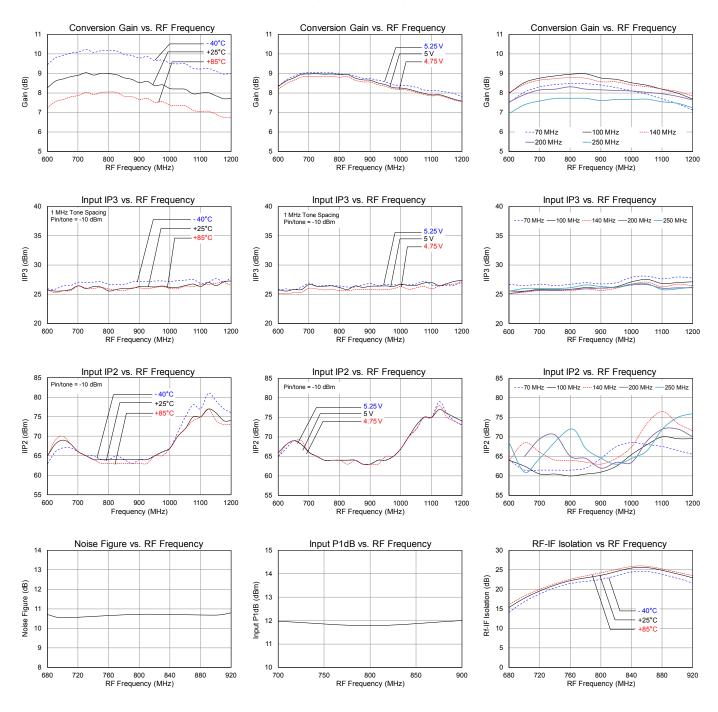

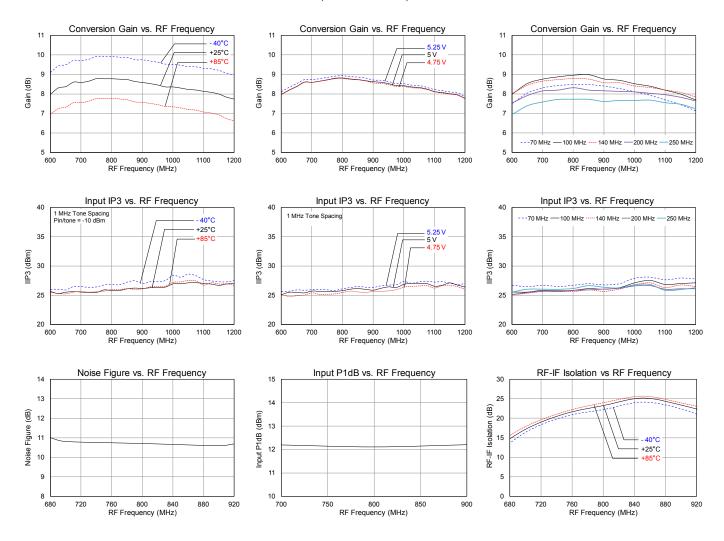

### Typical Performance Plots: Low-side LO with Standard Current Mode

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 680 MHz, IF = 140 MHz

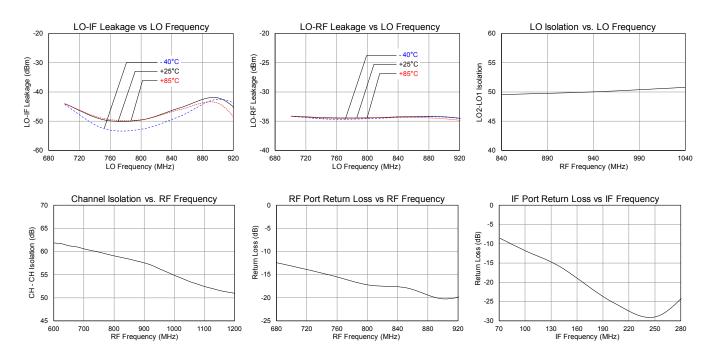

## Typical Performance Plots: Low-side LO with Standard Current Mode (cont.)

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 680 MHz, IF = 140 MHz

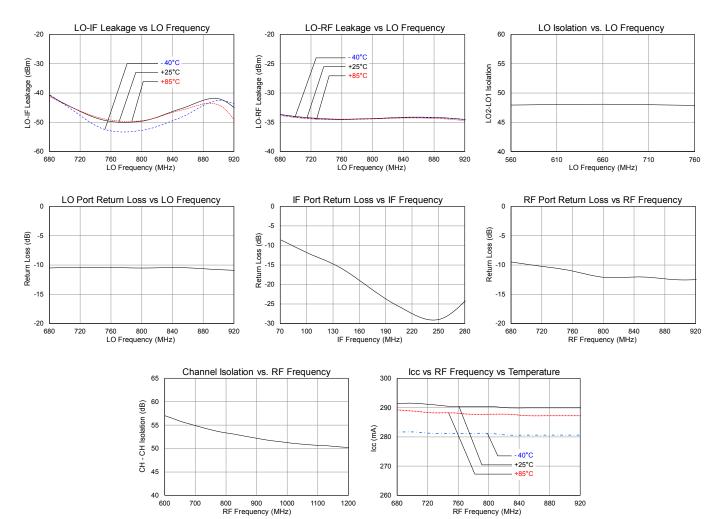

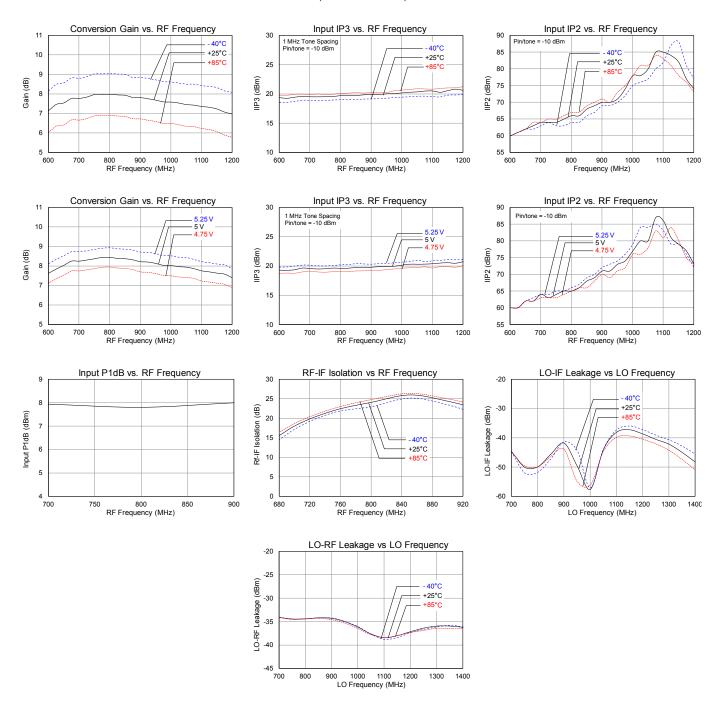

### **Typical Performance Plots: Low-side LO with Low Current Mode**

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 680 MHz, IF = 140 MHz

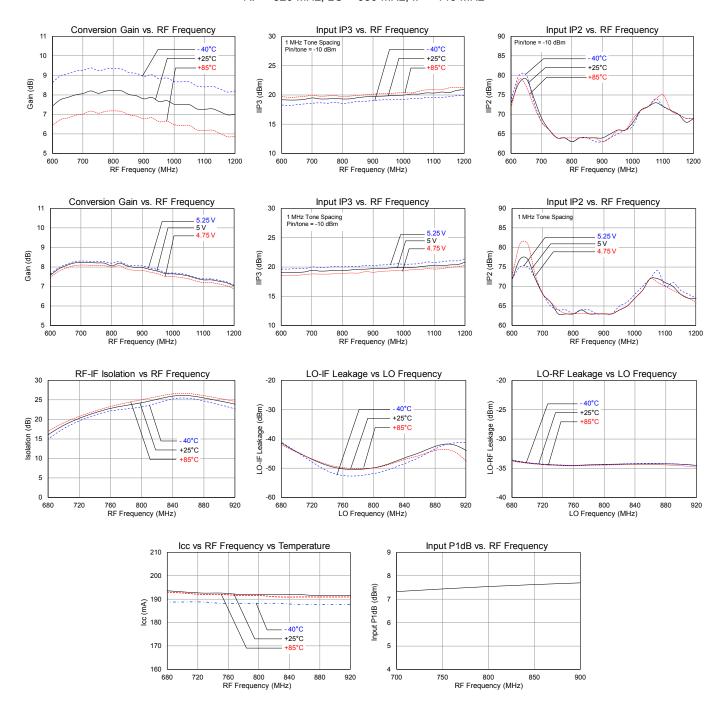

## Typical Performance Plots: High-side LO with Standard Current Mode

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 960 MHz, IF = 140 MHz

## Typical Performance Plots: High-side LO with Standard Current Mode (cont.)

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 960 MHz, IF = 140 MHz

## **Typical Performance Plots: High-side LO with Low Current Mode**

Test conditions unless otherwise noted: Vcc =+5V, Temp.=25°C, LSLO, Both Channels, LO power = 0 dBm RF = 820 MHz, LO = 960 MHz, IF = 140 MHz

## 680-920 MHz High IP3 Dual Channel Downconverter SEMICONDUCTOR

#### **Detailed Device Description**

The TQP519021 is a high-linearity diversity dual-channel down-converter designed to meet the demanding performance, functionality, and cost goals of current and next generation mobile infrastructure base stations. This device is fully integrated diversity mixer that includes LO switch, two stage LO drivers, high-linearity mixers, RF balun and IF amplifiers. A single pole double throw (SPDT) high isolation switch has been included to select between two different LO inputs for frequency hopping applications. IF amplifiers can be set to standard current or low current mode through logic input pins. The TQP519021 also integrates power down feature controlled by separate logic pin.

The single-ended RF input ports of both the main and diversity channels are internally matched to  $50\Omega$ , requiring no external matching components and DC-blocking capacitor. The RF input is internally transformed to a balanced signal using an internal, on-chip unbalanced-to-balanced (balun) transformer. The RF balun can support an RF input frequency range of 600-1200 MHz.

#### LO Drivers and LO switch

The TQP519021 is optimized for a 600MHz to 1100MHz LO frequency range. The two stage LO drivers allow the LO input power to be in the range of ±3 dBm. The LO section is optimized for low-side LO injection but also works for high-side LO applications with slightly degraded linearity performance.

As an added feature, a single pole double throw (SPDT) switch has been included to select between two different LO inputs for frequency hopping applications. The SPDT switch selects one of the two single-ended LO ports providing greater than 50 dB of LO1 to LO2 isolation. LO switching time is typically 100ns. The switch is controlled by a digital input (LOSEL), where logic-high selects LO1 and logic-low selects LO2. LO1 and LO2 inputs are internally matched to 50Ω, requiring only 100pF DC-blocking capacitors.

#### **Passive Double-Balanced Mixer**

The TQP519021 consists of a passive, double balanced, high-performance mixer that provides a very low conversion loss and high IIP3. Additionally, the balanced nature of the mixer provides for high channel to channel isolation.

#### IF Amplifiers

The TQP519021 has an IF frequency range of 70 – 280 MHz, where the low-end frequency depends on the frequency response of the external IF components. The IF amplifiers follow the passive mixers in the signal path and can be operated outside of this range, but with a slight degradation in performance. The outputs require a supply voltage connection using inductive chokes. The differential output impedance of the IF amplifier is approximately 200  $\Omega$ . If operation in a 50  $\Omega$  system is desired, the output can be transformed to 50  $\Omega$  by using a 4:1 transformer. One can use a differential IF amplifier on the mixer IF ports, but a DC block is required on both IFD+/IFD- and IFM+/IFM- ports to keep external DC from entering the IF ports of the mixer. These differential ports are ideal for providing better IIP2 performance.

#### **Standard Current Mode and Low Current Mode**

IF amplifiers can be set to standard current or low current mode through logic input pins. The IFD\_CURR\_SET and IFM\_CURR\_SET pins (17 and 29, respectively) are used to reduce the IF amplifier bias current. On the evaluation board, this is achieved by setting jumpers J10 and J12 as explained under Application Board section. The low current mode degrades IIP3 performance. The total current draw with low current mode is about 100mA lower than standard current mode. IFD\_CURR\_SET and IFM\_CURR\_SET pins can be left either NC or GND for the applications not using low current mode.

#### **Shutdown Mode**

The TQP519021 has additional integrated feature of power shut down for IF amplifiers and LO amplifier. The IFD SD and IFM SD pins (18 and 28, respectively) are used for IF amplifier shut down. The LOD SD and LOM SD pins (22 and 24, respectively) are used for LO amplifier shut down. On the evaluation board, this is achieved by setting jumpers J11, J13, J16 and J9 as explained under Application Board section. The total current draw during shut down mode is 3.5mA. The IFD SD and IFM\_SD pins can be left either NC or GND for the applications not using shutdown mode.

For any further technical questions, please email to sicapplications.engineering@tqs.com.

## **Pin Configuration and Description**

| Pin No.                                  | Symbol               | Description                                                                                                                                |  |

|------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                        | RFMAIN               | Main Channel RF Input. Internally matched to 50Ω. No external DC block required.                                                           |  |

| 4, 6                                     | VCC_LOM ,<br>VCC_LOD | DC Supply, +5V for LO amplifier. Bypass to GND with capacitor (0.1uF) as close as possi to the pin.                                        |  |

| 9                                        | RFDIV                | Diversity Channel RF Input. Internally matched to 50Ω. No external DC block required.                                                      |  |

| 13, 14                                   | IFD+, IFD-           | Diversity mixer differential IF Output. Pull up inductors connected to Vcc from each pin.                                                  |  |

| 16                                       | VCC_CTRL_D           | DC Supply, +5V for IF diversity amp. Bypass to GND with capacitor as close as possible to the pin.                                         |  |

| 17                                       | IFD_CURR_SET         | IF diversity amp bias control.                                                                                                             |  |

| 18                                       | IFD_SD               | IF diversity amp current shut down                                                                                                         |  |

| 19                                       | LO1                  | Local oscillator input 1. Internally matched to 50Ω. External DC block required.                                                           |  |

| 21                                       | Vcc                  | DC Supply, +5V for LO Switch. Bypass to GND with capacitor as close as possible to the pin.                                                |  |

| 22                                       | LOD_SD               | LO diversity amp current shut down                                                                                                         |  |

| 23                                       | LOSEL                | Local oscillator select.                                                                                                                   |  |

| 24                                       | LOM_SD               | LO main amp current shut down                                                                                                              |  |

| 27                                       | LO2                  | Local oscillator input 2. Internally matched to 50Ω. External DC block required.                                                           |  |

| 28                                       | IFM_SD               | IF main amp current shut down                                                                                                              |  |

| 29                                       | IFM_CURR_SET         | IF main amp bias control.                                                                                                                  |  |

| 30                                       | VCC_CTRL_M           | DC Supply, +5V for IF main amp. Bypass to GND with capacitor as close as possible to the pin.                                              |  |

| 32, 33                                   | IFM+, IFM-           | Main mixer differential IF Output. Pull up inductors connected to Vcc from each pin.                                                       |  |

| 2,8,10,11,35,36,<br>3,5,7,12,15,25,31,34 | NC                   | No internal connection. These pins can be GND or NC on the PCB.                                                                            |  |

| 20, 26                                   | GND                  | RF ground. These pins must be grounded to achieve the noted RF performance.                                                                |  |

| Backside Paddle                          | RF/DC GND            | RF/DC ground. Use recommended via pattern to minimize inductance and thermal resistance; see PCB Mounting Pattern for suggested footprint. |  |

#### **Mechanical Information**

### **Package Marking and Dimensions**

Marking: Part number - TQP519021

Year, week, country code - YYWW CCCC

Assembly code – AaXXXX

#### Notes:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. Except where noted, this part outline conforms to JEDEC standard MO-270, Issue B (Variation DAE) for extra thin profile, fine pitch, internal stacking module (ISM).

- 3. Dimension and tolerance formats conform to ASME Y14.4M-1994.

- 4. The contact pin numbering convention and pin 1 identifier conform to JESD 95-1 SPP-012.

- 5. Co-planarity applies to the exposed ground/thermal pad as well as the contact pins.

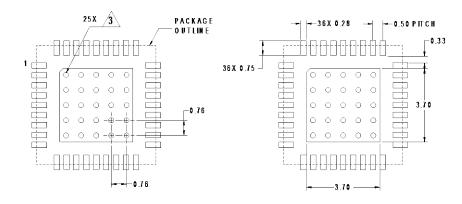

## **PCB Mounting Pattern**

#### NOTES:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. Use 1 oz. copper minimum for top and bottom layer metal.

- 3. Vias are required under the backside paddle of this device for proper RF/DC grounding and thermal dissipation. We recommend a 0.35mm (#80/.0135") diameter bit for drilling via holes and a final plated thru diameter of 0.25 mm (0.10").

- 4. Ensure good package backside paddle solder attach for reliable operation and best electrical performance.

## 680-920 MHz High IP3 Dual Channel Downconverter SEMICONDUCTOR

### **Product Compliance Information**

#### **ESD Sensitivity Ratings**

#### **Caution! ESD-Sensitive Device**

ESD Rating: Class 1B

Value: Passes ≥ 500V to < 1000V

Test: Human Body Model (HBM)

Standard: JEDEC Standard JESD22-A114

ESD Rating: Class IV

Value: Passes ≥ 1000 V

Test: Charged Device Model (CDM)

Standard: JEDEC Standard JESD22-C101

#### **MSL Rating**

MSL Rating: Level 3

Test: 260°C convection reflow

Standard: JEDEC Standard IPC/JEDEC J-STD-020

#### Solderability

Compatible with both lead-free (260 °C max. reflow temperature) and tin/lead (245 °C max. reflow temperature) soldering processes.

Package contact plating: Electrolytic plated Au over Ni

#### **RoHs Compliance**

This part is compliant with EU 2002/95/EC RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment).

This product also has the following attributes:

- Lead Free

- Halogen Free (Chlorine, Bromine)

- · Antimony Free

- TBBP-A (C<sub>15</sub>H<sub>12</sub>Br<sub>4</sub>0<sub>2</sub>) Free

- PFOS Free

- SVHC Free

#### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

Web: <u>www.triquint.com</u> Tel: +1.503.615.9000 Email: <u>info-sales@tgs.com</u> Fax: +1.503.615.8902

For technical questions and application information: Email: sjcapplications.engineering@tgs.com

#### **Important Notice**

The information contained herein is believed to be reliable. TriQuint makes no warranties regarding the information contained herein. TriQuint assumes no responsibility or liability whatsoever for any of the information contained herein. TriQuint assumes no responsibility or liability whatsoever for the use of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for TriQuint products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

TriQuint products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.