# Programmable Gain Amplifier PRELIMINARY DATA SHEET - Rev 1.1

#### **FEATURES**

- High Linearity, High Output Power Integrated Amplifier with Programmable Gain Control

- Attenuation Range: 0-58 dB, Adjustable in 2 dB Increments via a 3-wire Serial Control

- · 33 dB Gain (at Minimum Attenuation)

- Low Distortion Products at Output Power Levels up to +64 dBmV

- · Low Noise Figure and Output Noise

- Frequency range: 5-85 MHz

- 5 V Operation

- Materials set consistent with RoHS Directives.

Surface Mount Package

#### **APPLICATIONS**

- DOCSIS 3.0 Data Cable Modems and E-MTAs

- CATV Set Top Boxes

#### PRODUCT DESCRIPTION

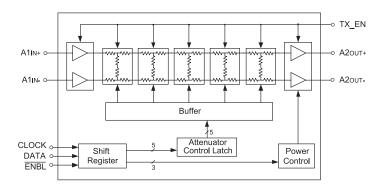

The ARA2017 is a highly linear, high output power, programmable gain amplifier optimized for DOCSIS 3.0 cable modem and E-MTA applications. Using a low noise input amplification stage and an ultra linear output driver amplifier, the device generates extremely low distortion products at the high output power levels required by DOCSIS 3.0 signals. Its balanced circuit design provides superior harmonic performance and an integrated digitally-controlled, multiple-stage precision step attenuator enables system solutions to meet DOCSIS power step accuracy requirements.

The ARA2017 supports output power levels of +64 dBmV while minimizing harmonic, distortion, and output noise levels. Its precision attenuator provides up to 58 dB of attenuation in 2 dB increments, which is set by programming the register via a 3-wire serial interface. The output stage current, a feature which allows the device to be operated in reduced power modes for extended backup battery life, is also programmed through the 3-wire serial interface. The ARA2017 is offered in a 28-pin 5 mm x 5 mm x 1 mm QFN package.

Figure 1: Functional Block Diagram

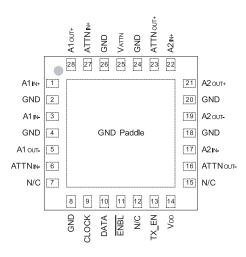

Figure 2: Pinout (X-Ray Top View)

Table 1: Pin Description

| PIN | NAME                 | DESCRIPTION                                              | PIN | NAME                 | DESCRIPTION                        |

|-----|----------------------|----------------------------------------------------------|-----|----------------------|------------------------------------|

| 1   | A1 <sub>IN+</sub>    | Amplifier A1 (+) Input                                   | 28  | А1оит+               | Amplifier A1 (+) Output and Supply |

| 2   | GND                  | Ground                                                   | 27  | ATTN <sub>IN</sub> + | Attentuator Input (+)              |

| 3   | A1ıN-                | Amplifier A1 (-) Input                                   | 26  | GND                  | Ground                             |

| 4   | GND                  | Ground                                                   | 25  | Vattn                | Attenuator Supply                  |

| 5   | А1оит-               | Amplifier A1 (-) Output and Supply                       | 24  | GND                  | Ground                             |

| 6   | ATTN <sub>IN</sub> - | Attentuator Input (-)                                    | 23  | ATTNout+             | Attentuator Output (+)             |

| 7   | N/C                  | No Connection                                            | 22  | A2ıN+                | Amplifier A2 (+) Input             |

| 8   | GND                  | Ground                                                   | 21  | A2out+               | Amplifier A2 (+) Output and Supply |

| 9   | CLOCK                | Clock                                                    | 20  | GND                  | Ground                             |

| 10  | DATA                 | Data                                                     | 19  | <b>А2</b> оит-       | Amplifier A2 (-) Output and Supply |

| 11  | ENBL                 | Enable                                                   | 18  | GND                  | Ground                             |

| 12  | N/C                  | No Connection (Reserved for future use - leave floating) | 17  | A2 <sub>IN-</sub>    | Amplifier A2 (-) Input             |

| 13  | TX_EN                | Transmit Enable                                          | 16  | ATTNout-             | Attentuator Output (-)             |

| 14  | V <sub>DD</sub>      | Supply                                                   | 15  | N/C                  | No Connection                      |

## **ELECTRICAL CHARACTERISTICS**

**Table 2: Absolute Minimum and Maximum Ratings**

| PARAMETER                                                                    | MIN  | MAX                  | UNIT | COMMENTS                       |

|------------------------------------------------------------------------------|------|----------------------|------|--------------------------------|

| Supply: V <sub>DD</sub> (pins 5, 14, 19, 21, 28), V <sub>ATTN</sub> (pin 25) | 0    | +6                   | V    |                                |

| RF Power at Inputs (pins 1, 3)                                               | 1    | +40                  | dBmV | differential into 200 $\Omega$ |

| Digital Interface (pins 9, 10, 11, 13)                                       | -0.5 | V <sub>DD</sub> +0.5 | V    |                                |

| Storage Temperature                                                          | -55  | +150                 | °C   |                                |

Stresses in excess of the absolute ratings may cause permanent damage. Functional operation is not implied under these conditions. Exposure to absolute ratings for extended periods of time may adversely affect reliability.

**Table 3: Operating Ranges**

| PARAMETER                                        | MIN  | TYP | MAX             | UNIT |

|--------------------------------------------------|------|-----|-----------------|------|

| Operating Frequency (f)                          | 5    | 1   | 85              | MHz  |

| Supply: V <sub>DD</sub> (pins 5, 14, 19, 21, 28) | +4.5 | +5  | +5.5            | V    |

| Digital Interface (pins 9, 10, 11, 13)           | 0    | -   | $V_{\text{DD}}$ | V    |

| Case Temperature (Tc)                            | -40  | +25 | +85             | °C   |

The device may be operated safely over these conditions; however, parametric performance is guaranteed only over the conditions defined in the electrical specifications.

Table 4: Digital Interface Specifications  $(V_{DD} = +5.0 \text{ V})$

| PARAMETER                          | MIN  | TYP | MAX             | UNIT |

|------------------------------------|------|-----|-----------------|------|

| Logic High Input Voltage: Vın,нідн | +2.0 | =   | V <sub>DD</sub> | V    |

| Logic Low Input Voltage: VIN,LOW   | 0    | -   | +0.8            | V    |

Note:

<sup>1.</sup> Logic control levels apply to the 3-wire programming bus (pins 9, 10, 11) and the transmit enable control (pin 13).

# Table 5: Electrical Specifications ( $V_{DD}$ = +5.0 V, $T_X$ Enabled (unless otherwise noted), $T_C$ = 25 °C)

| PARAMETER                                                                                            | MIN    | TYP            | MAX      | UNIT    | COMMENTS                                                       |

|------------------------------------------------------------------------------------------------------|--------|----------------|----------|---------|----------------------------------------------------------------|

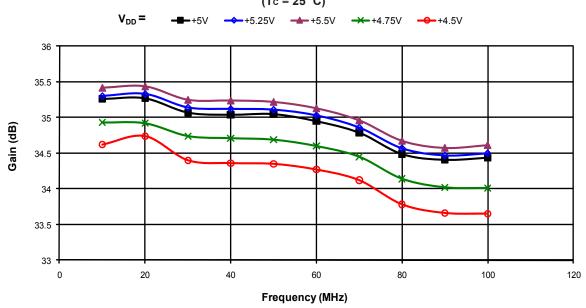

| Gain (1)                                                                                             | 34     | 36             | 37       | dB      | 0 dB attenuation setting                                       |

| Gain Flatness (1)                                                                                    | -<br>- | 0.5<br>1.0     | -        | dB      | 5 to 42 MHz<br>5 to 85 MHz                                     |

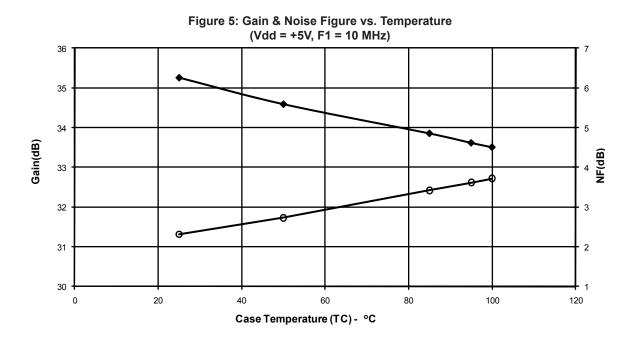

| Gain Variation over Temperature                                                                      | -      | -0.02          | -        | dB/°C   |                                                                |

| Gain Range with Attenuator                                                                           | 58     | -              | -        | dB      |                                                                |

| Incremental Attenuator Step Size                                                                     | 1.5    | 2              | 2.5      | dB      |                                                                |

| 2 <sup>nd</sup> Harmonic Distortion Level (1) (2)                                                    | -      | -67            | -55      | dBc     | +64 dBmV into 75 $\Omega$                                      |

| 3 <sup>rd</sup> Harmonic Distortion Level (1) (2)                                                    | -      | -72            | -55      | dBc     | +64 dBmV into 75 $\Omega$                                      |

| 3rd Order Output Intercept (1)(2)                                                                    | +88    | +93            | -        | dBmV    | 2 tone, +61 dBmV/tone                                          |

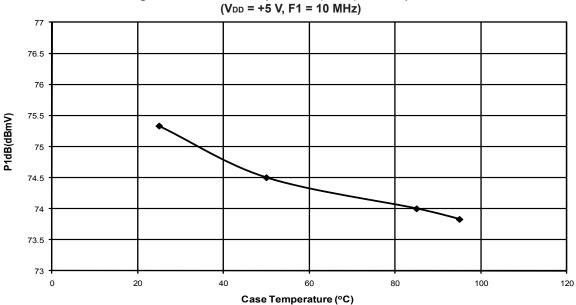

| 1 dB Gain Compression (1) (2)                                                                        | -      | +73            | -        | dBmV    |                                                                |

| Noise Figure (1) (2)                                                                                 | -      | 2.5            | -        | dB      | Full gain @ 0 dB attenuator setting; Includes input balun loss |

| Output Noise Power<br>Active / No Signal / Min. Atten. Set.<br>Active / No Signal / Max. Atten. Set. | -<br>- | -38.5<br>-53.8 | 1 1      | dBmV    | Any 160 kHz bandwidth from 5 to 85 MHz                         |

| Isolation (85 MHz) in Tx disable mode                                                                | -      | 60             | -        | dB      |                                                                |

| Differential Input Impedance                                                                         | -      | 200            | 1        | Ω       | between pins 1 and 3<br>(Tx enabled)                           |

| Differential Output Impedance                                                                        | -      | 75             | -        | Ω       | between pins 19 and 21                                         |

| Output Impedance                                                                                     | -      | 75             | 1        | Ω       | with transformer                                               |

| Output Return Loss<br>(75 Ohm characteristic impedance)                                              | -      | -15<br>-12     | 1 1      | dB      | Tx enabled<br>Tx disabled                                      |

| Output Voltage Transient<br>Tx enable / Tx disable                                                   | -      | 50<br>7        |          | mVp-p   | 0 dB attenuator setting<br>24 dB attenuator setting            |

| Total Supply Current (1) (2) (pins 5, 14, 19, 21, 25, 28)                                            | -      | 340<br>10.5    | 400<br>- | mA      | Tx enabled (TX_EN high) Tx disabled (TX_EN low)                |

| Total Power Consumption                                                                              | -<br>- | 1.7<br>52.5    | -        | W<br>mW | Tx enabled (TX_EN high) Tx disabled (TX_EN low)                |

#### Notes:

<sup>(1)</sup> As measured in ANADIGICS test fixture.

<sup>(2)</sup> Measured using the maximum current setting-see Application Information section.

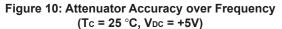

# **DATA PLOTS**

Figure 3: Gain vs. Frequency over Voltage ( $Tc = 25 \,^{\circ}C$ )

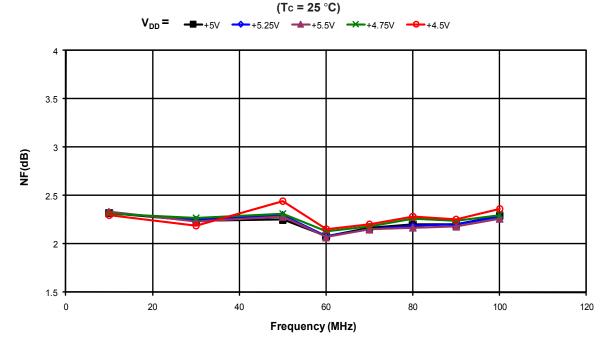

Figure 4: Noise Figure vs. Frequency over Voltage

Figure 6: 1dB Gain Compression (P1dB) vs. Voltage (Tc = 25  $^{\circ}$ C, F1 = 10 MHz) 77 76.5 76 75.5 75 74.5 74 73.5 73 4.8 5.4 4.4 4.6 5.2 5.6

P1dB (dBmV)

Voltage (Vdc)

Figure 7: 1dB Gain Compression (P1dB) vs. Temperature ( $V_{DD} = +5 \text{ V}$ , F1 = 10 MHz)

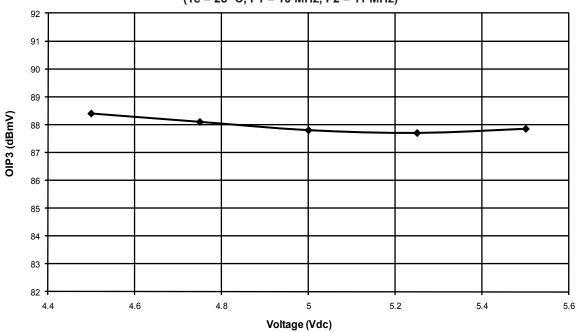

(V<sub>dd</sub> = +5 Vdc, F1 = 10 MHz, f2 = 11 MHz) OIP3(dBmV) Case Temperature(°C)

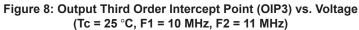

Figure 7: Output Third Order Intercept Point (OIP3) vs Temperature

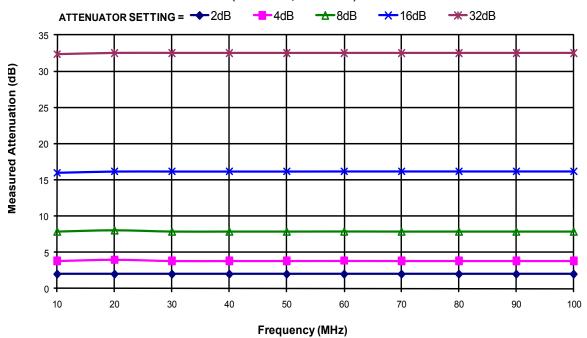

Figure 11:Attenuator Accuracy over Voltage (Tc = +25 °C, F1 = 10 MHz)

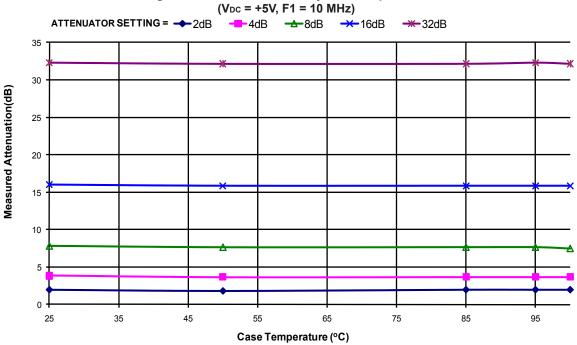

Figure 12: Attenuator Accuracy over Temperature

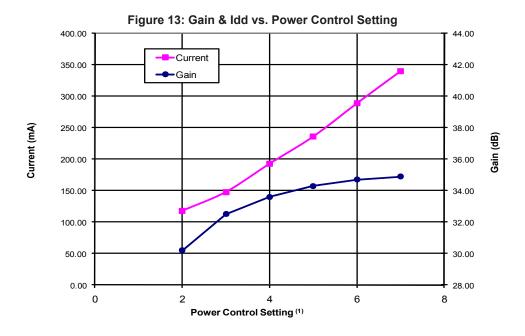

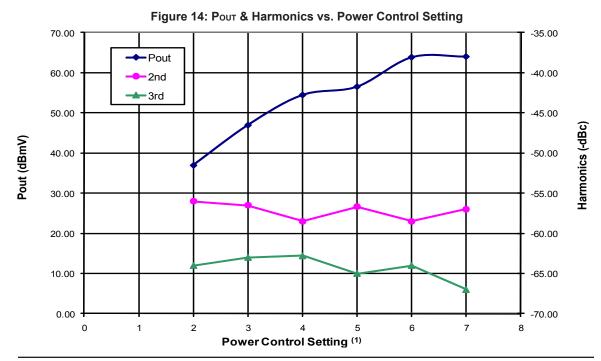

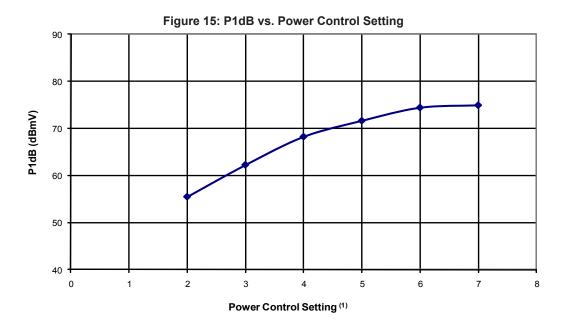

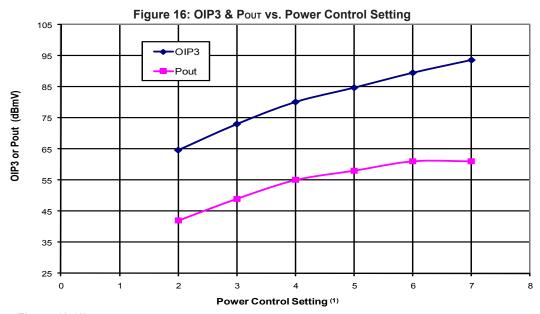

Notes (Figures 13-16):

(1.) Power control setting refers to the programming register bits 7, 8, and 9 (see Table 6). The power control can be set using ANADIGICS Tuner Control Software, version 1.2.3, in the "Advanced settings" window. The software is used in conjunction with the ANADIGICS ARA2017 evaluation board.

Note: Pin 12 is reserved for future use. Do not connect (leave floating).

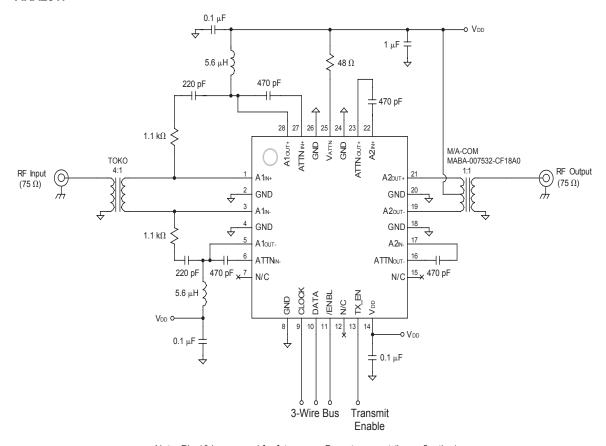

Figure 17: Test Circuit

#### Notes:

1. Pin 12 is reserved for future use. Do not connect (leave floating).

(2) Input balun is used for evaluation test purposes only in 75  $\Omega$  system. Actual application does not require a 4:1 balun on the input.

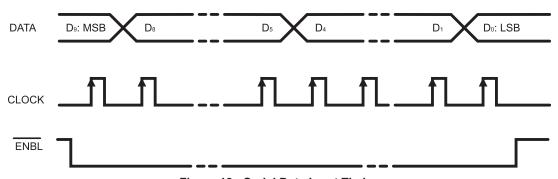

#### LOGIC PROGRAMMING

## **Programming Instructions**

The programming word is set through a 10 bit shift register via the data, clock and enable lines. The data is entered in order with the most significant bit (MSB) first and the least significant bit (LSB) last. The

enable line must be low for the duration of the data entry, then set high to latch the shift register. The rising edge of the clock pulse shifts each data value into the register.

**Table 6: Programming Register**

| DATA BIT | 9 | 8       | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|----------|---|---------|---|---|---|------|---|---|---|---|

| FUNCTION |   | Current |   |   | = | Gain |   |   | 0 | 1 |

#### Notes:

- 1. Refer to Application Information section for Current and Gain bit settings.

- 2. Data bit 0 should always be set to "1".

- 3. Data bit 1 is reserved for future use, and should be set to "0".

Figure 18: Serial Data Input Timing

#### APPLICATION INFORMATION

#### Transmit Enable / Disable

The ARA2017 can be switched on (Tx enable) and off (Tx disable) via an asynchronous input TX\_EN (pin 13). A logic high will turn the amplifier on. The gain and current settings are retained during Tx disable and do not need to be reloaded.

## Gain/Attenuator Setting

The gain of the ARA2017 can be controlled via the 3-wire bus. Data bits D2 through D6 set the gain/ attenuator level, with 00000 being the min gain setting, and 11111 being the max gain setting. A new gain/ attenuator setting can be loaded while the PGA is on (Tx enable), but will not take effect until TX\_EN has been cycled off /on.

#### **Output Stage Current Setting**

The ARA2017 consists of 2 gain stages. The input stage operates at a constant fixed current when Tx is enabled. The current in the output stage can be controlled via the 3-wire bus. Data bits D7 – D9 set the current. 111 will set the output stage to maximum current for maximum linearity. The current can be lowered for improved efficiency at lower output power levels, or lower linearity requirements. 000 will turn both stages off, the same as Tx disable. A new current setting can be loaded while the PGA is on (Tx Enable), but will not take effect until TX\_EN has been cycled off /on.

#### **Output Transformer**

Matching the balanced output of the ARA2017 to a single-ended 75  $\Omega$  load is accomplished using a 1:1 turns ratio transformer. In addition to the balanced to single-ended conversion, this transformer provides the bias to the output amplifier stage via the center tap.

The transformer also cancels even mode distortion products and common mode signals, such as the voltage transients that occur while enabling and disabling the amplifiers. As a result, care must be taken when selecting the transformer to be used at the output. It must be capable of handling the RF and DC power requirements without saturating the core, and it must have adequate isolation and good phase and amplitude balance. It also must operate over the desired frequency and temperature range for the intended application.

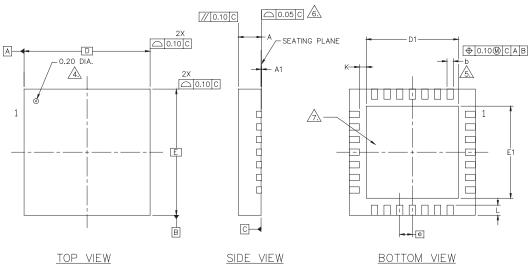

## **PACKAGE OUTLINE**

| S<br>M<br>B | DIMENSIONS-MM |      |       | s<br>M     | DIMENSION | S-INCHES | N <sub>o</sub> |

|-------------|---------------|------|-------|------------|-----------|----------|----------------|

| 10          | MIN.          | MAX. | NO TE |            | MIN.      | MAX.     | T <sub>E</sub> |

| Α           | 0.80          | 1.00 |       | Α          | 0.031     | 0.039    |                |

| A1          | 0.00          | 0.05 |       | A1         | 0.000     | 0.002    |                |

| Ь           | 0.18          | 0.30 |       | Ь          | 0.007     | 0.012    |                |

| D           | 5.00          |      | D     | 0.197      |           |          |                |

| D1          | 3.40          | 3.80 |       | D1         | 0.134     | 0.149    |                |

| E           | 5.00          | BSC  |       | E          | 0.197     | BSC      |                |

| E1          | 3.40          | 3.80 |       | E1         | 0.134     | 0.149    |                |

| e           | 0.50 BSC      |      |       | e          | 0.020 BSC |          |                |

| K           | 0.20          |      | K     | 0.007 MIN. |           |          |                |

| П           | 0.35          | 0.57 |       | П          | 0.014     | 0.022    |                |

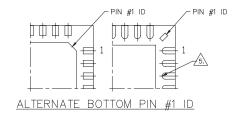

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. MAX. PACKAGE WARPAGE IS 0.05 mm.

- 3. MAXIMUM ALLOWABLE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- A PIN #1 ID ON TOP WILL BE LASER MARKED.

- DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30mm FROM TERMINAL TIP. RADIUS OPTIONAL. DIMENSION 6 SHOULD NOT BE MEASURED IN RADIUS AREA.

- BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 7. REFERENCE JEDEC OUTLINE MO-220.

Figure 19: S29 Package Outline - 28 Pin 5 mm x 5 mm x 1 mm QFN

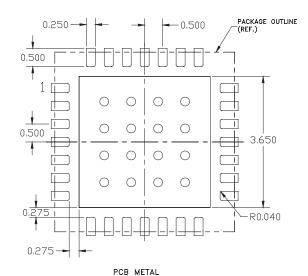

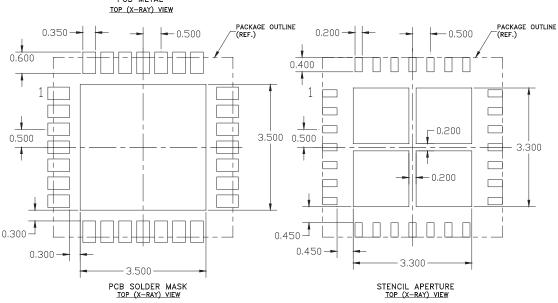

#### NOTES:

- (1) UNLESS SPECIFIED DIMENSIONS ARE SYMMETRICAL ABOUT CENTER LINES SHOWN.

- (2) DIMENSIONS IN MILLIMETERS.

- (3) NUMBER OF THERMAL VIAS

REQUIRED FOR EFFICIENT HEAT

REMOVAL DEPENDENT ON THE PCB

PROCESS CAPABILITY. VIAS SHOWN

FOR REFERENCE ONLY

Figure 20: Land Pattern

#### ORDERING INFORMATION

| ORDER         | TEMPERATURE      | PACKAGE                                  | COMPONENT PACKAGING                 |

|---------------|------------------|------------------------------------------|-------------------------------------|

| NUMBER        | RANGE            | DESCRIPTION                              |                                     |

| ARA2017RS29P8 | -40 °C to +85 °C | 28 Pin QFN Package<br>5 mm x 5 mm x 1 mm | Tape and Reel, 2500 pieces per Reel |

#### ANADIGICS, Inc.

141 Mount Bethel Road Warren, New Jersey 07059, U.S.A.

Tel: +1 (908) 668-5000 Fax: +1 (908) 668-5132

URL: http://www.anadigics.com E-mail: Mktg@anadigics.com

#### **IMPORTANT NOTICE**

ANADIGICS, Inc. reserves the right to make changes to its products or to discontinue any product at any time without notice. The product specifications contained in Advanced Product Information sheets and Preliminary Data Sheets are subject to change prior to a product's formal introduction. Information in Data Sheets have been carefully checked and are assumed to be reliable; however, ANADIGICS assumes no responsibilities for inaccuracies. ANADIGICS strongly urges customers to verify that the information they are using is current before placing orders.

#### WARNING

ANADIGICS products are not intended for use in life support appliances, devices or systems. Use of an ANADIGICS product in any such application without written consent is prohibited.