## **17-24 GHz Linear Driver Amplifier**

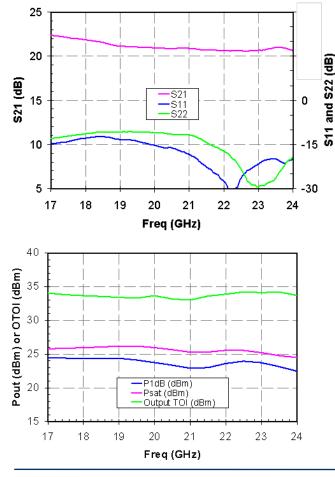

## **Measured Performance**

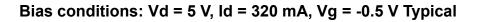

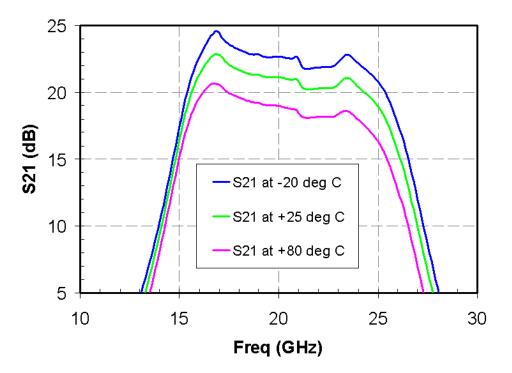

Bias conditions: Vd = 5 V, Id = 320 mA, Vg = -0.5 V Typical

## **Key Features**

- Frequency Range: 17-24 GHz

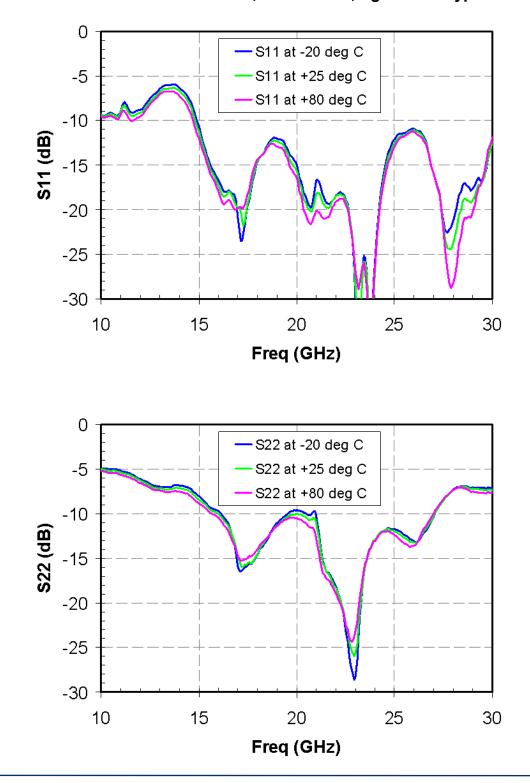

- 25.5 dBm Nominal Psat, 23.5 dBm Nominal P1dB

- Gain: 20 dB

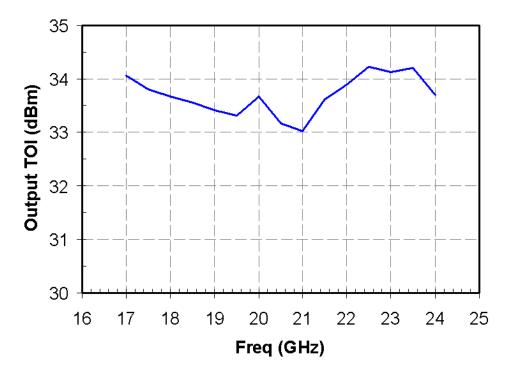

- OTOI: 33 dBm Typical

- Bias: Vd = 5 V, Idq = 320 mA, Vg = -0.5 V Typical

- Package Dimensions: 4 x 4 x 0.85 mm

## Primary Applications

- Point-to-Point Radio

- Point-to-Multipoint Communications

## **Product Description**

The TriQuint TGA2521-SM is a three stage HPA MMIC design using TriQuint's proven 0.25 um Power pHEMT process. The TGA2521-SM is designed to support a variety of millimeter wave applications including point-to-point digital radio and other K band linear gain applications.

The TGA2521-SM provides 23.5 dBm nominal output power at 1dB compression across 17-24GHz. Typical small signal gain is 20 dB at 17GHz and 20dB at 23GHz.

The TGA2521-SM requires minimum off-chip components. Each device is DC and RF tested for key parameters. The device is available in a 4x4mm plastic QFN package.

Lead-free and RoHS compliant.

Datasheet subject to change without notice.

1

TriQuint Semiconductor: www.triguint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tgs.com

## Absolute Maximum Ratings 1/

Table I

|          |                             | · -       |            |

|----------|-----------------------------|-----------|------------|

| Symbol   | Parameter                   | Value     | Notes      |

| Vd-Vg    | Drain to Gate Voltage       | 11 V      |            |

| Vd1, Vd2 | Drain Voltage               | 8 V       | <u>2</u> / |

| Vg1, Vg2 | Gate Voltage Range          | -5 to 0 V |            |

| ld1      | Drain Current               | 115 mA    | <u>2</u> / |

| ld2      | Drain Current               | 407 mA    | <u>2</u> / |

| lg1      | Gate Current Range          | 8 mA      |            |

| lg2      | Gate Current Range          | 34 mA     |            |

| Pin      | Input Continuous Wave Power | 23 dBm    | <u>2</u> / |

| Tchannel | Channel Temperature         | 200 °C    |            |

- 1/ These ratings represent the maximum operable values for this device. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device and / or affect device lifetime. These are stress ratings only, and functional operation of the device at these conditions is not implied.

- 2/ Combinations of supply voltage, supply current, input power, and output power shall not exceed the maximum power dissipation listed in Table IV.

## Table II Recommended Operating Conditions

| Symbol   | Parameter <u>1</u> /         | Value  |

|----------|------------------------------|--------|

| Vd1, Vd2 | Drain Voltage                | 5 V    |

| ld1+ld2  | Drain Current                | 320 mA |

| Id_Drive | Drain Current under RF Drive | TBD mA |

| Vg1      | Gate #1 Voltage              | -0.5 V |

| Vg2      | Gate #2 Voltage              | -0.5 V |

<u>1</u>/ See assembly diagram for bias instructions.

Table III RF Characterization Table

Bias: Vd = 5 V, Id = 320 mA, Vg = -0.5 V, typical

| SYMBOL | PARAMETER                                    | TEST<br>CONDITIONS  | MIN  | NOM   | MAX  | UNITS |

|--------|----------------------------------------------|---------------------|------|-------|------|-------|

| Gain   | Small Signal Gain                            | f = 17.7 – 23.6 GHz | 18.5 | 20    | 23.5 | dB    |

| IRL    | Input Return Loss                            | f = 17.7 – 23.6 GHz |      | 14    |      | dB    |

| ORL    | Output Return Loss                           | f = 17.7 – 23.6 GHz |      | 12    |      | dB    |

| Psat   | Saturated Output<br>Power <u>1</u> /         | f = 17.7 – 23.6 GHz | 23   | 25.5  |      | dBm   |

| P1dB   | Output Power @<br>1dB Compression <u>1</u> / | f = 17.7 – 23.6 GHz | 21   | 23.5  |      | dBm   |

| ΤΟΙ    | Output TOI                                   | f = 17.7 – 23.6 GHz | 30   | 33    |      | dBm   |

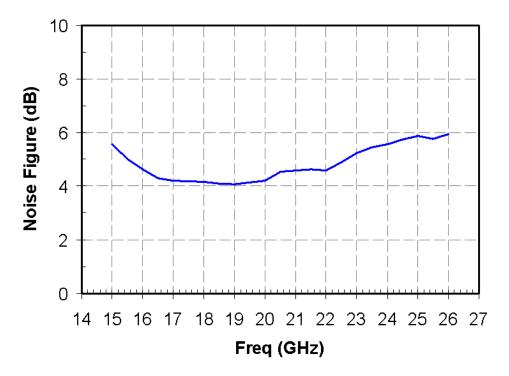

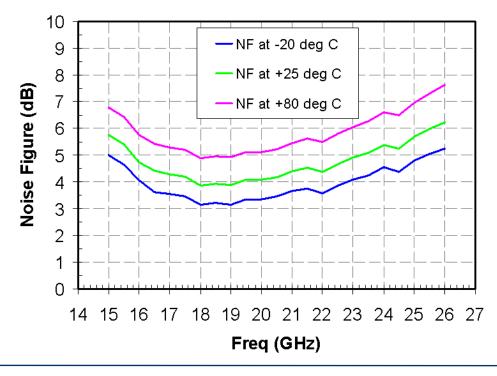

| NF     | Noise Figure                                 | f = 17.7 – 23.6 GHz |      | 5     | 7    | dB    |

|        | Gain Temperature<br>Coefficient              | f = 17.7 – 23.6 GHz |      | -0.04 |      | dB/°C |

|        | Power Temperature<br>Coefficient             | f = 17.7 – 23.6 GHz |      | -0.01 |      | dB/°C |

<u>1</u>/ Psat and P1dB measurements performed with Vg held constant. Drain current increases under RF drive.

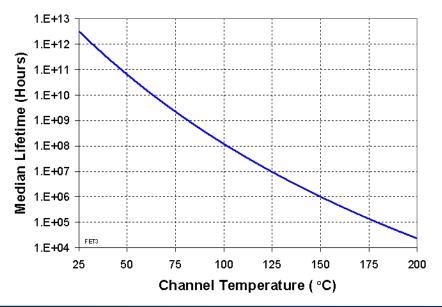

## Table IV

**Power Dissipation and Thermal Properties**

| Parameter                                 | Test Conditions                                         | Value                                                   | Notes         |

|-------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------|

| Maximum Power Dissipation                 | Tbaseplate = 85 °C                                      | Pd = 3.9 W<br>Tchannel = 200 °C                         | <u>1/ 2</u> / |

| Thermal Resistance, θjc                   | Vd = 5 V<br>Id = 320 mA<br>Pd = 1.6 W                   | θjc = 29.5 °C/W<br>Tchannel = 127 °C<br>Tm = 7.7E+6 Hrs |               |

| Thermal Resistance, θjc<br>Under RF Drive | Vd = 5 V<br>Id = TBD mA<br>Pout = TBD dBm<br>Pd = TBD W | θjc = TBD °C/W<br>Tchannel = TBD °C<br>Tm = TBD Hrs     |               |

| Mounting Temperature                      | 30 Seconds                                              | 320 °C                                                  |               |

| Storage Temperature                       |                                                         | -65 to 150 °C                                           |               |

1/ For a median life of 1E+6 hours, Power Dissipation is limited to

$Pd(max) = (150 \circ C - Tbase \circ C)/\theta jc.$

2/ Channel operating temperature will directly affect the device lifetime. For maximum life, it is recommended that channel temperatures be maintained at the lowest possible levels.

## Median Lifetime (Tm) vs. Channel Temperature

**TGA2521-SM**

6

#### **Measured Data**

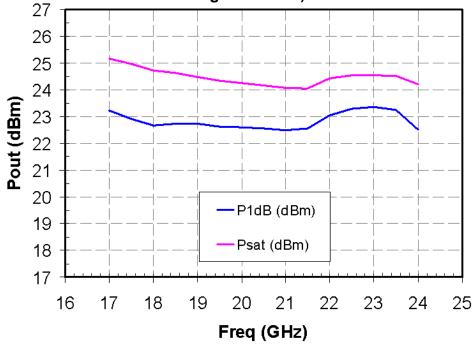

Bias conditions: Vd = 5 V, Id = 320 mA, Vg = -0.5 V Typical

**TGA2521-SM**

# Bias conditions: Vd = 5 V, Idq = 320 mA, Vg = -0.5 V (Vg held constant from small signal to Psat)

Bias conditions: Vd = 5 V, Id = 320 mA, Vg = -0.5 V (Id held constant from small signal to Psat)

## **TGA2521-SM**

9

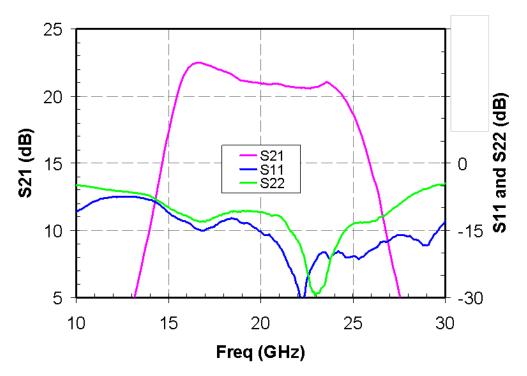

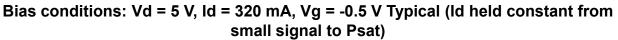

#### **Measured Data**

**TGA2521-SM**

Bias conditions: Vd = 5 V, Id = 320 mA, Vg = -0.5 V Typical

Bias conditions: Vd = 5 V, Id = 320 mA, Vg = -0.5 V Typical

TriQuint Semiconductor: www.triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com Sep 2012 © Rev E

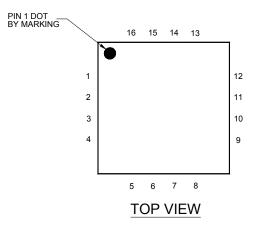

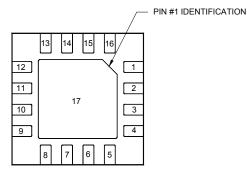

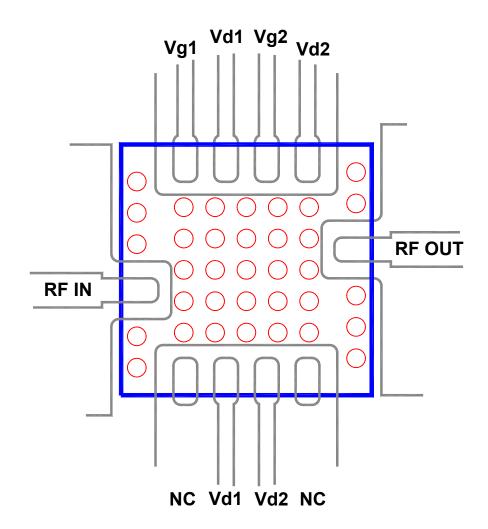

## Package Pinout

BOTTOM VIEW

#### SIDE VIEW

| Pin                                                              | Symbol               | Description                                                                                                                                       |

|------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                                                                | RF In                | Input, matched to 50 ohms.                                                                                                                        |

| 11                                                               | RF Out               | Output, matched to 50 ohms.                                                                                                                       |

| 16                                                               | Vg1                  | Gate voltage for amplifier's input stage. 1/                                                                                                      |

| 14                                                               | Vg2                  | Gate voltage for amplifier's 2 <sup>nd</sup> and final stages. 1/                                                                                 |

| 6,15                                                             | Vd1 (bot), Vd1 (top) | Drain voltage for amplifier's input stage. Must be biased from both sides. 1/                                                                     |

| 7,13                                                             | Vd2 (bot), Vd2 (top) | Drain voltage for amplifier's 2 <sup>nd</sup> and final stages.<br>Must be biased from both sides. 1/                                             |

| 1,2,4,9,10,12 NC                                                 |                      | No internal connection. Must be grounded to the PCB. See 'Recommended Land Pattern'.                                                              |

| 5,8 GND Connected to 17 internally. Can be grou open on the PCB. |                      | Connected to 17 internally. Can be grounded or left open on the PCB.                                                                              |

| 17 GND                                                           |                      | Backside paddle. Multiple vias on the PCB should<br>be employed to minimize inductance and thermal<br>resistance. See 'Recommended Land Pattern'. |

1/ Bias network required. See 'Recommended Application Circuit' .

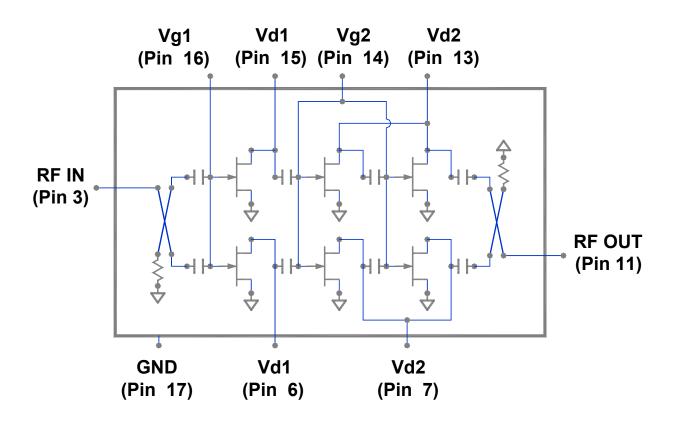

### **Electrical Schematic**

### **Bias Procedures**

#### Bias-up Procedure

Vg1, Vg2 set to -1.5 V

Vd1, Vd2 set to +5 V

Reduce Vg1, Vg2 to -1.5V. Ensure Id ~ 0 mA

Adjust Vg1, Vg2 more positive until Id is 320 mA. This will be  $\sim$  Vg = -0.5 V

Turn Vd1, Vd2 to 0 V

**Bias-down Procedure**

Turn off RF supply

Apply RF signal to input

Turn Vg1, Vg2 to 0 V

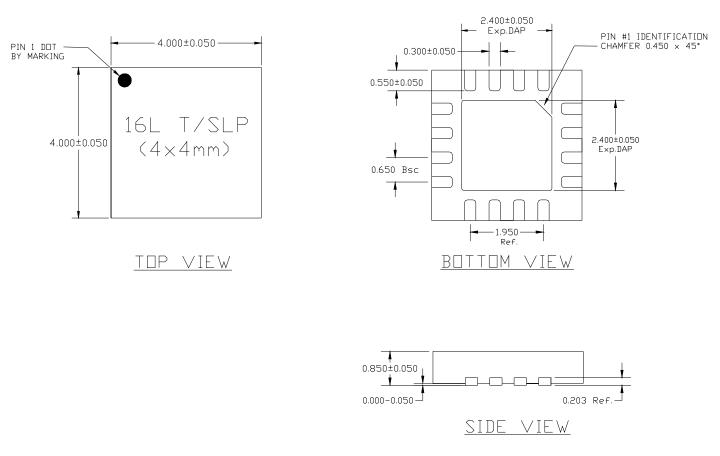

## **Mechanical Drawing**

Units: millimeters Thickness: 0.85 Pkg x,y size tolerance: +/- 0.050 Package edge to bond pad dimensions are shown to center of pad

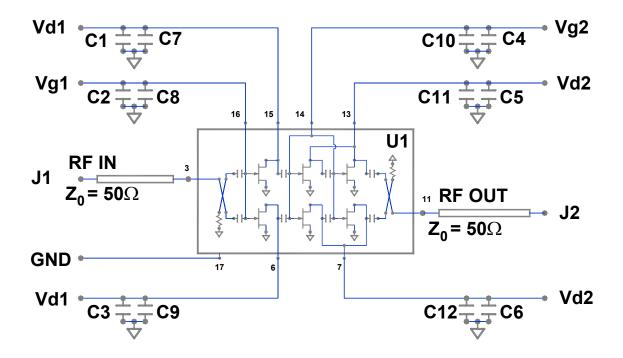

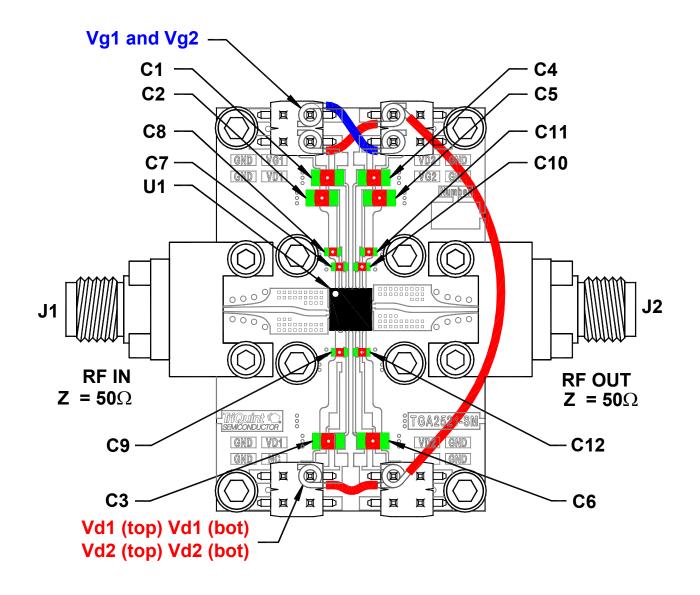

**Recommended Application Circuit**

| Ref Designator       | Value      | Description                              |

|----------------------|------------|------------------------------------------|

| U1                   |            | TriQuint TGA2521-SM                      |

| C1 C2 C3 C4 C5 C6    | 1.0 μF     | 1206 SMT Ceramic Capacitor               |

| C7 C8 C9 C10 C11 C12 | 0.01 μF    | 0603 SMT Ceramic Capacitor               |

| J1, J2               | 1092-01A-5 | Southwest Microwave End Launch Connector |

### **Recommended Assembly Diagram**

Board Material: 10 mil thick Rogers 4350

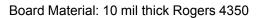

### **Recommended Land Pattern**

Open Plated Vias in Center of Land pattern; Vias are 12 mil Diameter, 20 mil center-to-center spacing

### **Assembly Notes**

Recommended Surface Mount Package Assembly

- Proper ESD precautions must be followed while handling packages.

- Clean the board with acetone. Rinse with alcohol. Allow the circuit to fully dry.

- TriQuint recommends using a conductive solder paste for attachment. Follow solder paste and reflow oven vendors' recommendations when developing a solder reflow profile. Typical solder reflow profiles are listed in the table below.

- Hand soldering is not recommended. Solder paste can be applied using a stencil printer or dot placement. The volume of solder paste depends on PCB and component layout and should be well controlled to ensure consistent mechanical and electrical performance.

- Clean the assembly with alcohol.

| <b>Reflow Profile</b>                | SnPb                        | Pb Free                     |  |

|--------------------------------------|-----------------------------|-----------------------------|--|

| Ramp-up Rate                         | 3 °C/sec                    | 3 °C/sec                    |  |

| Activation Time and Temperature      | 60 – 120 sec @ 140 – 160 °C | 60 – 180 sec @ 150 – 200 °C |  |

| Time above Melting Point             | 60 – 150 sec                | 60 – 150 sec                |  |

| Max Peak Temperature                 | 240 °C                      | 260 °C                      |  |

| Time within 5 °C of Peak Temperature | 10 - 20  sec                | 10 – 20 sec                 |  |

| Ramp-down Rate                       | 4-6 °C/sec                  | 4-6 °C/sec                  |  |

### **Ordering Information**

| Part                      | Package Style                              |

|---------------------------|--------------------------------------------|

| TGA2521-SM, TAPE AND REEL | 4mm x 4mm QFN Surface Mount, TAPE AND REEL |