# 2-16GHz, Power-Selectable Wideband Amplifier

### **Features**

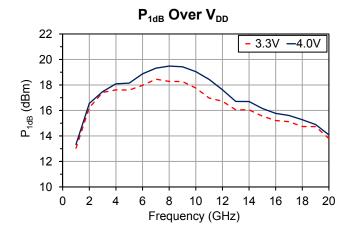

- Power-selectable from 7 to 18dBm P<sub>1dB</sub> by choosing bond option

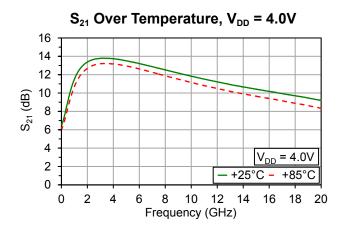

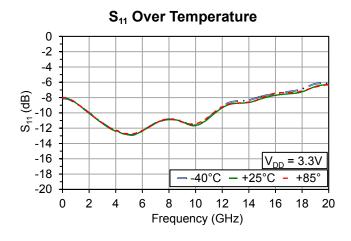

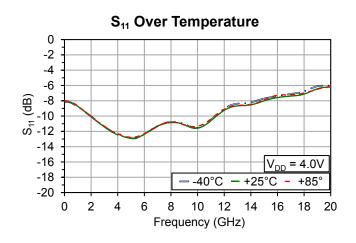

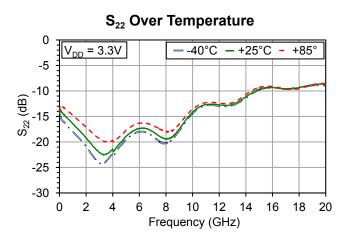

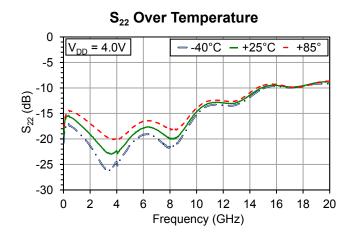

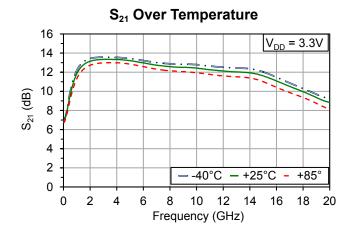

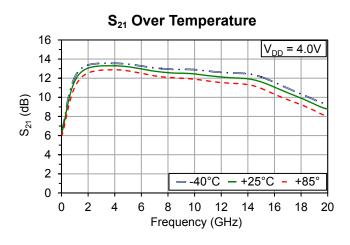

- Gain varies <1.2dB from -40°C to +85°C</li>

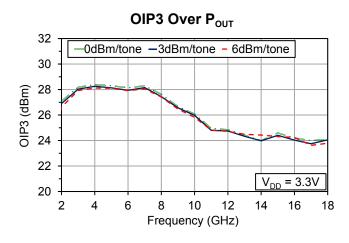

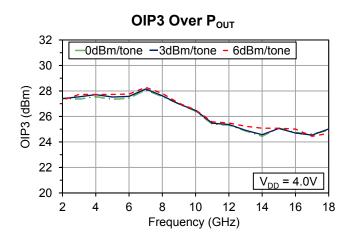

- Gain of ~10-14dB and ~28dBm OIP3 at the highest power option

- · Self-biased with single positive supply

- Input and Output matched to 50Ω

- 0.76mm x 0.66mm x 0.1mm die size

### **Applications**

- Instrumentation

- Electronic warfare

- Microwave communications

- Radar

RF Specifications (CW, Typical Device, RF Probe):  $T_A = 25$ °C,  $V_{DD} = 4$ V

| Bond Option  | ID | Gain | P1dB | OIP3     |

|--------------|----|------|------|----------|

| None         | 95 | 11.5 | 18.0 | 26.0     |

| R1 to Ground | 65 | 10.8 | 15.5 | 23.5 est |

| R2 to Ground | 36 | 9.0  | 7.5  | 15.5 est |

| R3 to Ground | 23 | 8.0  | 5.5  | 13.5 est |

**Table 1: Absolute Maximum Ratings, Not Simultaneous**

| Parameter                                       | Value        | Units |

|-------------------------------------------------|--------------|-------|

| Drain Voltage (V <sub>D</sub> )                 | +4.5         | V     |

| Input Power (P <sub>IN</sub> )                  | TBD (est +6) | dBm   |

| Operating Channel Temperature                   | 150¹         | °C    |

| Operating Ambient Temperature (T <sub>A</sub> ) | -55 to +85   | °C    |

| Storage Temperature                             | -65 to 150   | °C    |

| Thermal Resistasnce, Channel to Die Backside    | TBD          | °C/W  |

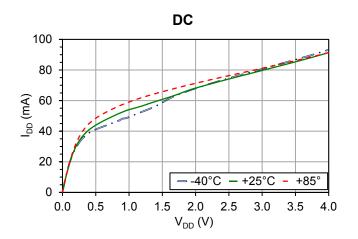

Table 2: Specifications (CW, 100% Test):  $T_A = 25$ °C,  $V_{DD} = 4V$

| Parameter                              | Min | Тур | Max | Units |

|----------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> , bond option = "none" | 45  | 95  | 135 | mA    |

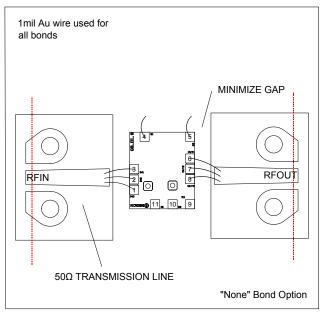

# RF Probe Measurement Set-Up With Reference Planes<sup>2</sup>

To use the "none" bonding option, attach the die directly to the baseplate.

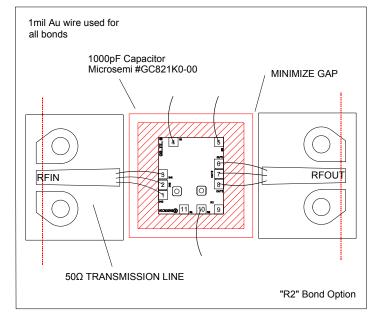

To use the "R1", "R2" or "R3" bonding options, mount the die on top of a capacitor to float the source and bond the appropriate pad to ground.

$<sup>^{1}</sup>$  MTTF > 10 $^{8}$  hours at T<sub>C</sub> = 150 $^{\circ}$ C

<sup>&</sup>lt;sup>2</sup> Reference planes are the same for S-parameter files downloadable on www.microsemi.com/mmics

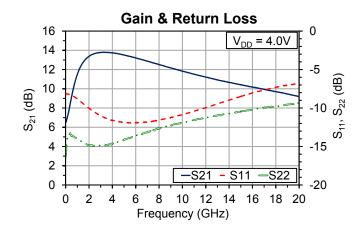

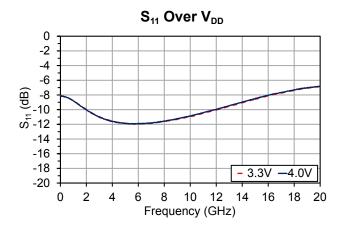

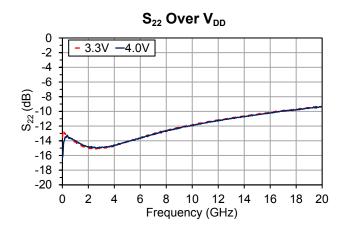

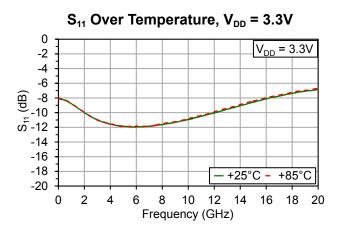

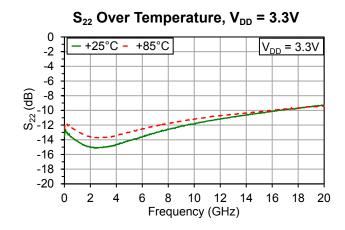

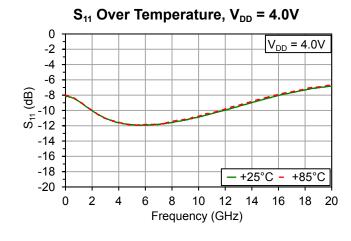

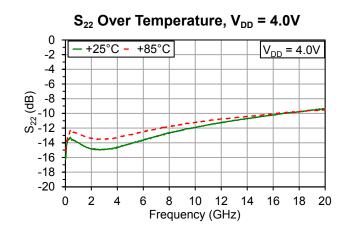

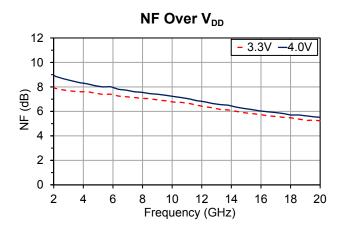

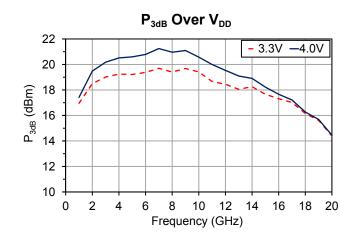

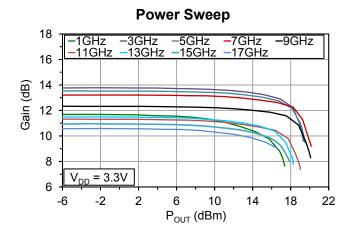

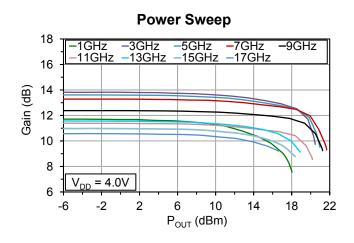

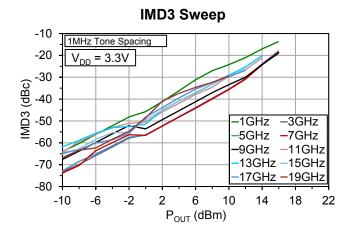

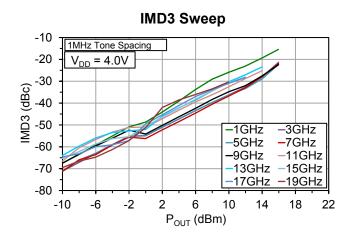

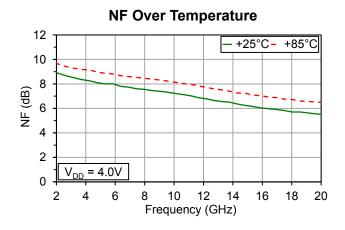

Typical Performance, RF Probe  $V_{DD}$  = 4V,  $I_{DD}$  = 95mA,  $T_A$  = 25°C, bond option = "none" unless otherwise noted

Typical Performance, RF Probe  $V_{DD}$  = 4V,  $I_{DD}$  = 95mA,  $T_A$  = 25°C, bond option = "none" unless otherwise noted

Typical Performance, RF Probe  $V_{DD}$  = 4V,  $I_{DD}$  = 95mA,  $T_A$  = 25°C, bond option = "none" unless otherwise noted

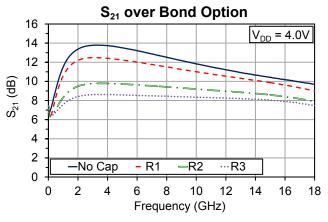

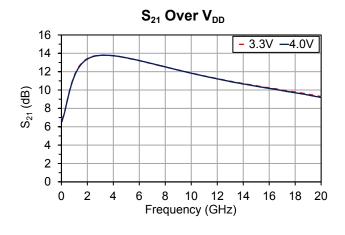

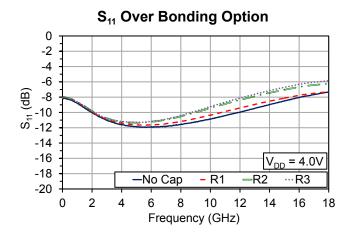

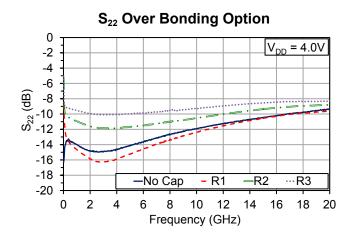

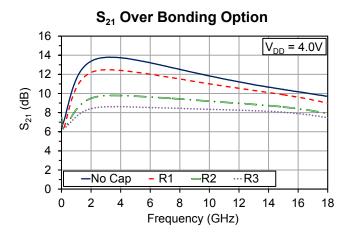

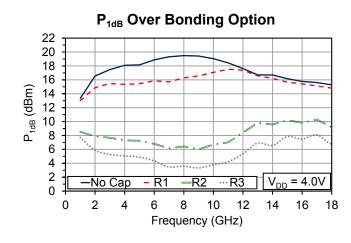

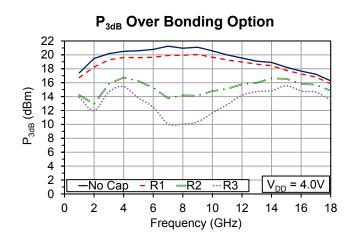

# Typical Performance, RF Probe

$V_{DD} = 4V$ ,  $I_{DD} = 95$ mA,  $T_A = 25$ °C, performance over bond option

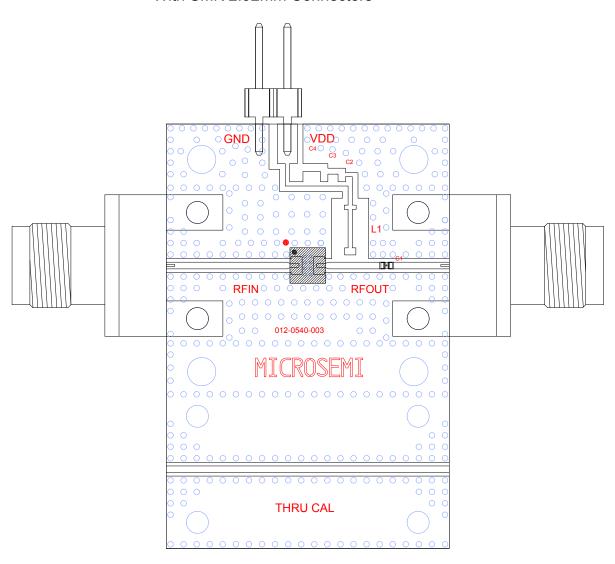

## **Connectorized Test Fixture**

With SMK 2.92mm Connectors

# Typical Performance, Connectorized Test Fixture

$V_{DD} = 4V$ ,  $I_{DD} = 95$ mA,  $T_A = 25$ °C, bond option = "none" unless otherwise noted

# Typical Performance, Connectorized Test Fixture $V_{DD}$ = 4V, $I_{DD}$ = 95mA, $T_A$ = 25°C, bond option = "none" unless otherwise noted

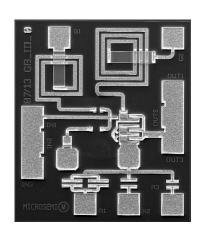

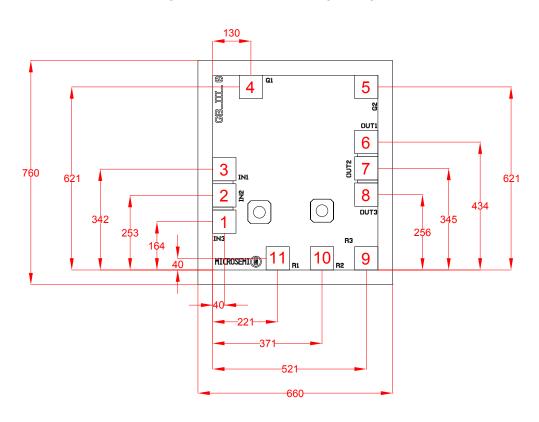

## Chip layout showing pad locations.

All dimensions are in microns. Die thickness is 100 microns. Backside metal is gold, bond pad metal is gold. Refer to Die Handling Application Note MM-APP-0001 (visit www.microsemi.com/mmics). See Page 2 for example bonding configurations.

**Table 3: Pad Descriptions**

| Pad #        | Description                       | Pad Dimensions (µm) |

|--------------|-----------------------------------|---------------------|

| 1, 2, 3      | RF <sub>IN</sub> , DC coupled     | 75 x 75             |

| 4, 5         | Ground                            | 75 x 75             |

| 6, 7, 8      | RF <sub>OUT</sub> , DC coupled    | 75 x 75             |

| 9            | R3 bond option                    | 75 x 75             |

| 10           | R2 bond option                    | 75 x 75             |

| 11           | R1 bond option                    | 75 x 75             |

| Die Backside | Refer to bonding option on page 2 | -                   |

### **Biasing**

MMA017AA is a self-biased device with a single positive supply. Apply  $V_{DD}$  to RF<sub>OUT</sub>.

Information contained in this document is proprietary to Microsem. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.